1.西安电子科技大学集成电路学部毫米波数字射频直接调制器芯片取得重要进展

2.信息工程大学李沛杰:晶圆级系统大芯片理论与设计 | 2024全球工程前沿

3.上海交大陈鹏课题组与许霄琰课题组在二维莫特绝缘体中发现量子自旋液体谱学证据

4.北京理工大学在“超高强多层核壳纳米结构增强铝锂合金铸件”领域取得重要突破

5.中国科学技术大学“祖冲之三号”创造新纪录 量子计算研究获新突破

1.西安电子科技大学集成电路学部毫米波数字射频直接调制器芯片取得重要进展

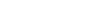

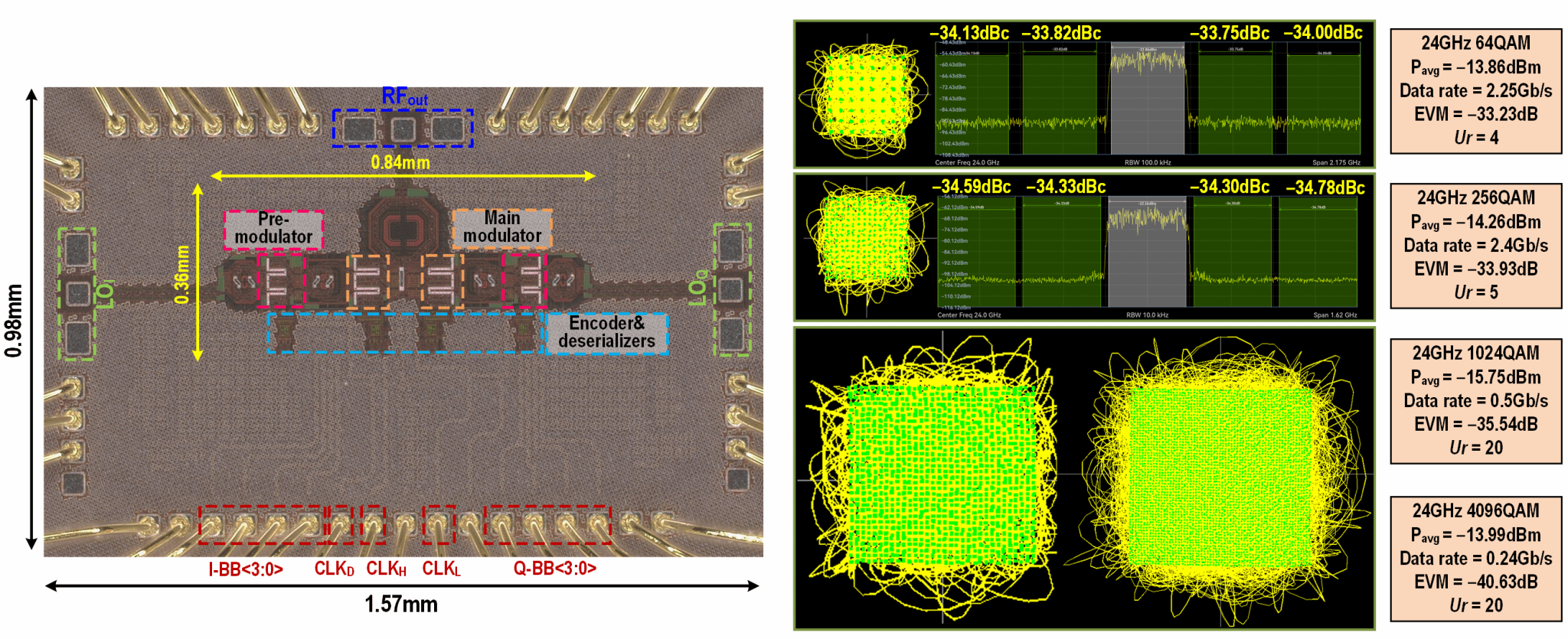

近日,西安电子科技大学集成电路学部INSPIRE实验室在毫米波数字射频直接调制器芯片方向取得重要进展。在集成电路设计领域国际顶级会议ISSCC(International Solid- State Circuits Conference)上发表了题为“A 21-to-31GHz DPD-less Quadrature RFDAC with Invariant Impedance and Scalable LO Leakage”的最新研究成果,西电为唯一完成单位,第一作者为钱慧珍教授,第一学生作者为硕士研究生秦梧博,杨银堂教授、钱慧珍教授为共同通信作者。该研究提出毫米波高线性度RFDAC新型架构,首次实现无数字预失真高阶调制、比特位可重构毫米波正交RFDAC,在21-31GHz工作频段下支持256QAM、1024QAM、4096QAM等无数字预失真宽带高阶调制。本研究为高线性度数字发射机研究开辟了新路线。

钱慧珍教授在ISSCC会议上作口头报告

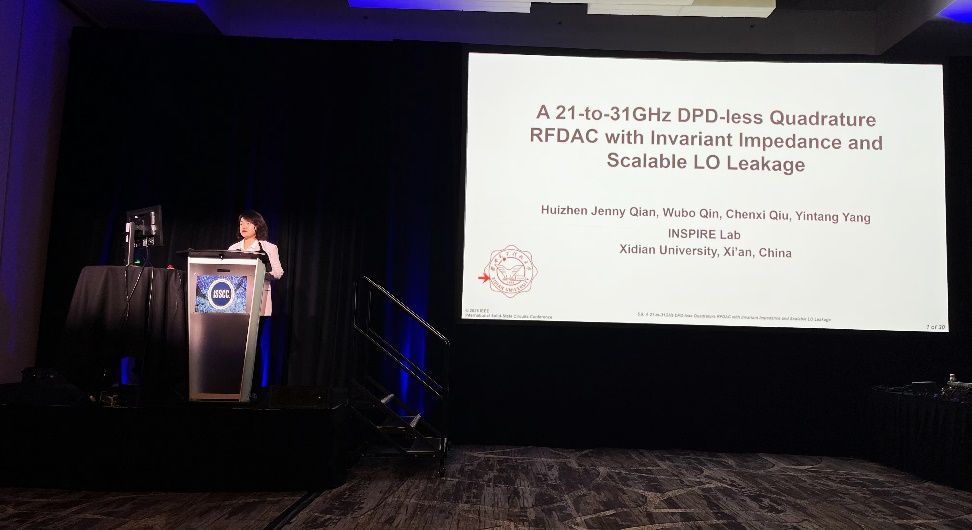

现代高速率无线通信系统对支持毫米波宽带高阶QAM调制的高性能射频前端芯片提出了迫切需求,如5G NR FR2,6G通信等。基于RFDAC的数字发射机相比传统模拟发射机架构,具有基带到射频直接转换、随工艺节点缩小而不断提升的射频性能、架构灵活、低功耗、高集成度等优势,采用时域和频域融合的设计理念,近十多年来取得飞速发展。然而,现有高速率数字发射机设计仍然存在一些挑战,存在的多种非线性来源限制了数据率的提升,如阻抗随控制码变化、本振泄露、工艺/电压/温度(PVT)变化、高速率基带信号失真、记忆效应、IQ失配等,且线性度在毫米波段进一步恶化。现有数字发射机线性化技术,如数字预失真、开环片上线性化技术、片上自校准环路等,存在硬件高复杂度、对频率或PVT变化不通用、需要额外的比特位以补偿ENOB损失、校准环路限制调制带宽等问题。

研究项目针对现有RFDAC输出阻抗随基带信号变化导致非线性,毫米波寄生效应导致线性度、本振泄露恶化,电路线性度对频率、PVT敏感等久未攻克的难题:(1)提出不变阻抗RFDAC架构,以数字化补偿阵列的方式实现阻抗恒定,其内在高线性度无需依赖对PVT及频率敏感的电路调参(器件、无源电路、偏置电压等)线性化方式,从根本上消除了RFDAC的阻抗变化非线性来源,因此其高线性度具有高鲁棒性、宽带特性;(2)提出可缩放本振泄露技术,采用前置数字预调制器的正交RFDAC架构进行本振信号的缩放,相比现有无源窄带本振泄露抵消的设计方法,具有宽带、高本振泄露抑制度等优势;(3)提出比特位可重构RFDAC架构,采用可重构串并转换器、可重构解码器、同步/异步切换等技术,实现无数字预失真2×8bit、非线性2×11bit两种工作模式。

采用阻抗补偿阵和预调制器的无数字预失真正交RFDAC原理

芯片显微照片及测试结果

基于40nm CMOS工艺,首次实现21-31GHz无数字预失真、可重构2×8bit/2×11bit正交RFDAC,支持 2.4Gb/s 256QAM、1024QAM、4096QAM等无数字预失真宽带高阶调制,具有内在高线性度、宽带、低功耗、高集成度、高数据率、比特位可重构的优势,实测调制带宽优于中电科思仪毫米波矢量信号源。相比此前工作于相近频段和相同数据率的RFDAC(有数字预失真),在相同数据率下(2.4Gb/s)EVM和ACLR提升了大于4dB。本研究工作得到了国家自然科学基金重大项目、优青项目的支持。(来源: 西安电子科技大学)

2.信息工程大学李沛杰:晶圆级系统大芯片理论与设计 | 2024全球工程前沿

晶圆级系统大芯片理论与设计是指领域专用软硬件协同的复杂系统设计基础理论和晶圆级高密度集成的设计方法,以及在此基础上应用系统与晶圆级芯片的高效映射和部署方案。晶圆级系统大芯片是基于晶圆级高密度集成工艺创新和软硬件协同结构创新实现的面向特定领域专用的信息系统物理形态。具备超高集成密度与超灵活功能部署的晶圆级系统大芯片通常具有超高的功能密度。晶圆级系统大芯片摆脱了传统微电子技术对先进制程的依赖,可通过异构异质集成、多光罩拼接和晶圆级键合等方式实现系统摩尔定律的延续,并通过软件定义体系结构赋能集成电路设计与应用全流程,实现多应用场景垂直整合和随阅历数据的自我演化。目前,晶圆级系统大芯片理论与设计的研究成果保持着高速迭代,并快速渗透到云计算、超算、智算等大型信息系统基础设施中。

晶圆级系统大芯片理论与设计为提升信息系统性能、效能与处理能力提供了理论基础,其主要研究方向包括领域专用软硬件协同架构和晶圆级集成工艺。领域专用软硬件协同架构是指面向领域应用共性特征,在计算系统设计和运行全流程中,通过统一的描述和工具对软件架构与硬件架构进行集成开发,跨越软硬件界面进行系统优化,确保软硬件协同工作与高效交互,实现更高的系统性能和效率的计算架构设计范式。晶圆级集成工艺基于先进集成技术与微电子理论,研究晶圆级键合、跨尺度高精度集成等工艺技术,设计晶圆级系统大芯片的硬件系统。

晶圆级系统大芯片理论与设计未来发展仍需解决可靠性设计与测试、应用部署优化、生成式晶上互连网络、系统广义鲁棒性技术四方面问题。首先,晶圆级系统大芯片需要更可靠的设计与测试技术来保障硬件系统的生产良率和运行可靠性。其次,应用部署优化技术亟须进一步优化,以实现复杂应用到硬件系统的高效映射。再次,晶上互连网络的生成式结构可为未来智能计算系统提供晶圆级系统大芯片底座。最后,晶圆级系统大芯片的系统广义鲁棒性技术可为未来信息系统基础设施新形态提供安全支撑。

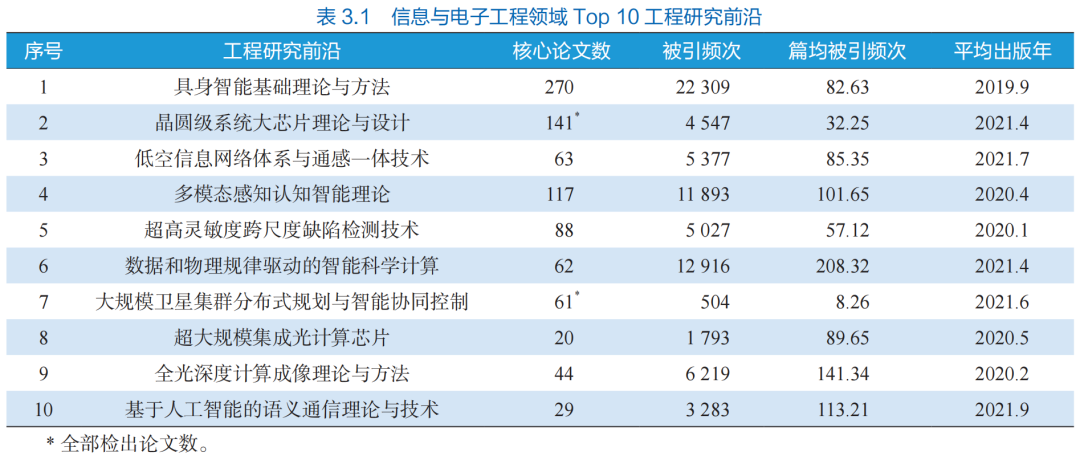

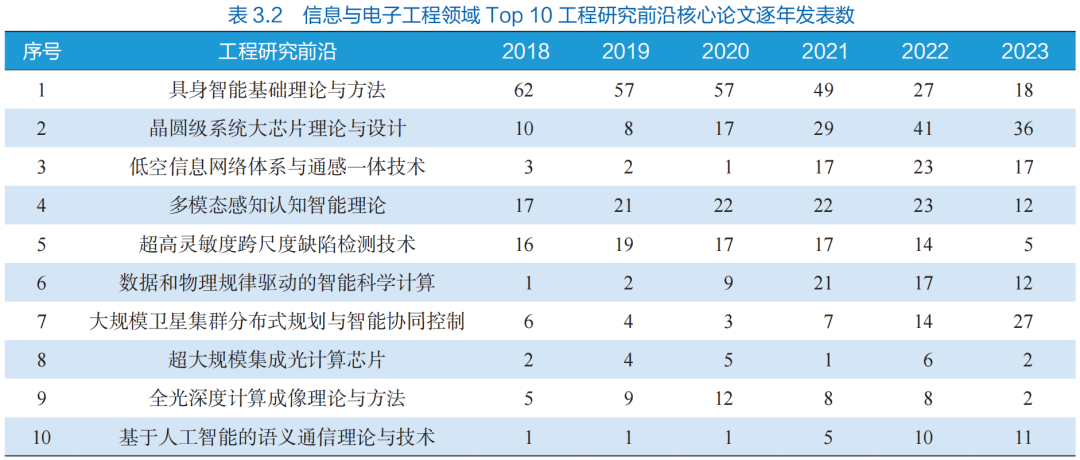

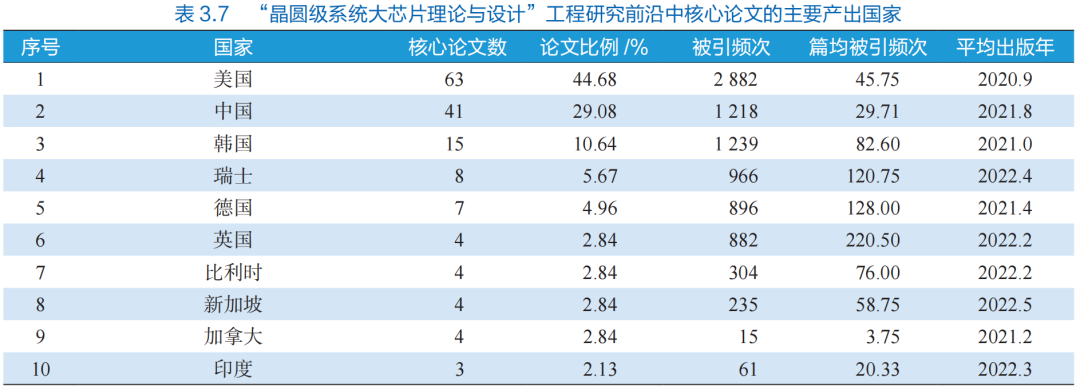

该前沿主题2018—2023年间发表的核心论文(注:针对该主题在Web of Science检索得到的被引频次位于前10%的高影响力论文——截至2023年12月)数量及其逐年发表情况见表3.1和表3.2。

晶圆级系统大芯片通过采用领域专用软硬件协同系统架构设计和晶圆级高密度集成方法的联合创新结构,实现领域内复杂应用到晶圆级系统大芯片硬件的映射,具有功能密度大、能效能重高、应用部署灵活等优点。然而,由于目前晶圆级系统大芯片资源规模大、结构复杂,且高度依赖先进集成工艺能力,芯粒之间功能协同难度大,晶圆级系统大芯片理论与设计亟须在理论架构和工艺实现两方面取得突破。

首先,在理论架构方面,主要呈现两大趋势。一是体系架构设计与应用任务深度融合。传统面向全领域应用的通算算力占比自2016年(95%)起逐步下降,预计到2030年将降至30%以下;而面向人工智能应用的智算算力占比则从2016年的3%迅速攀升,预计到2030年将达到70%以上。智能算力系统的体系架构设计一直与机器学习算法的演进紧密绑定并深度融合。二是软硬件协同,包括协同设计、协同仿真、协同运行与协同评估等。相比于通用计算系统软硬件解耦实现面向全领域计算一切可计算问题、专用计算系统软硬件一体实现面向专门应用最大限度提升性能与效能,软硬件协同在保持系统灵活性的基础上可实现计算综合能力的大幅提升。

其次,在工艺实现方面,一个重要的发展方向是晶圆级硅基板设计与实现工艺,旨在解决晶圆级互连硅基板的制备难题,进而提升异构集成系统的设计空间;另一个发展方向是高密度高精度集成工艺,需先突破异构异质芯粒到晶圆级硅基板的高密度键合工艺以及高密度晶圆级供电和散热工艺,再通过跨尺度高精度集成工艺实现晶圆、供电、散热等微系统到系统的可靠组装。这一方向的主要研究机构包括加州大学洛杉矶分校、伊利诺伊大学、台湾积体电路制造股份有限公司、清华大学、中国科学院微电子研究所、法国原子能委员会电子与信息技术实验室(CEA-Leti)等。

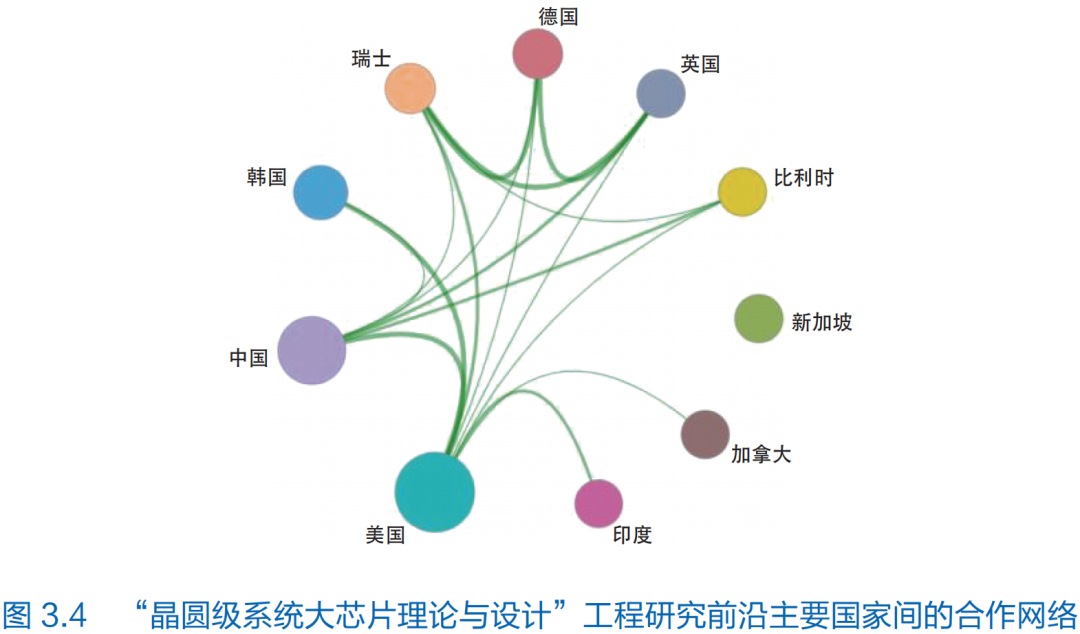

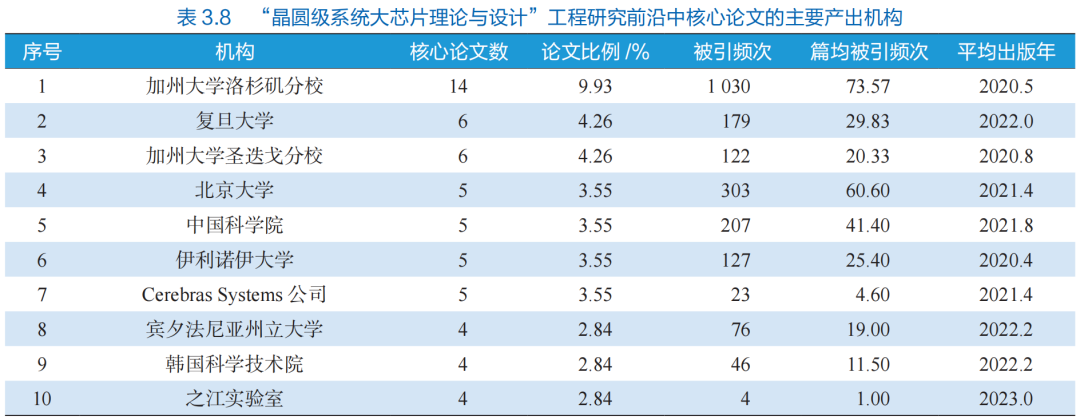

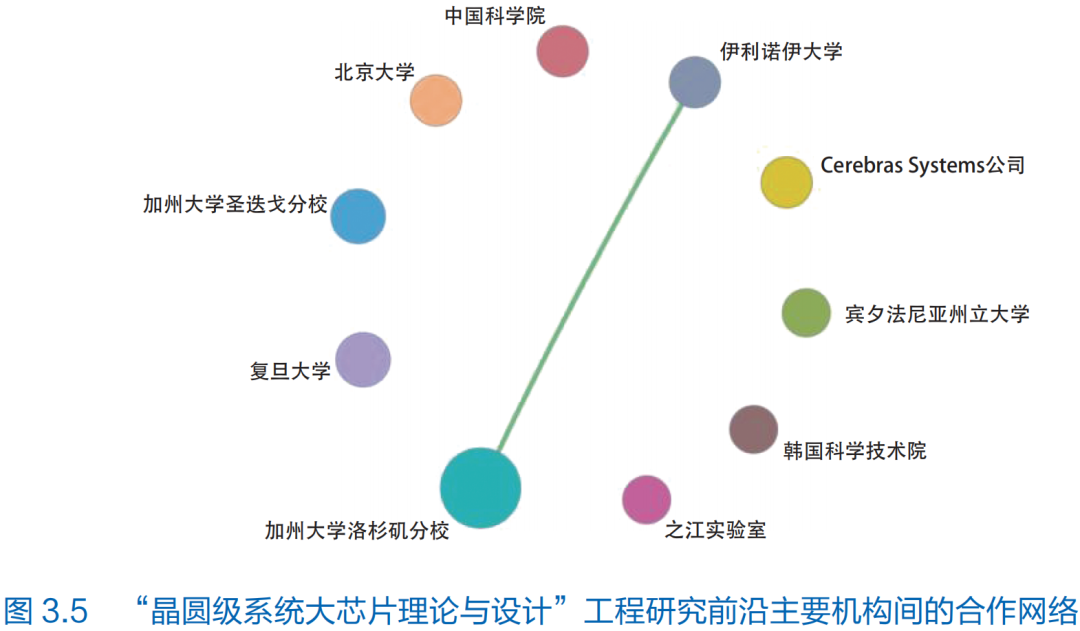

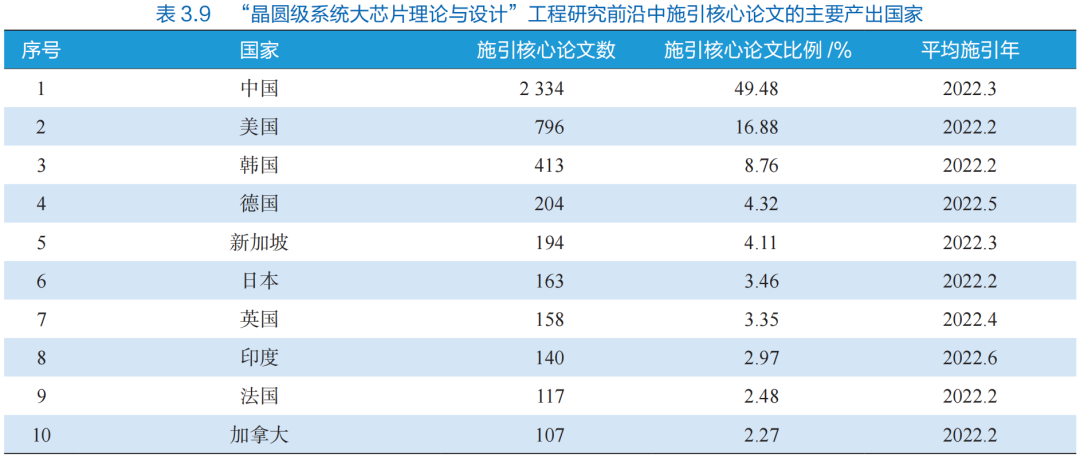

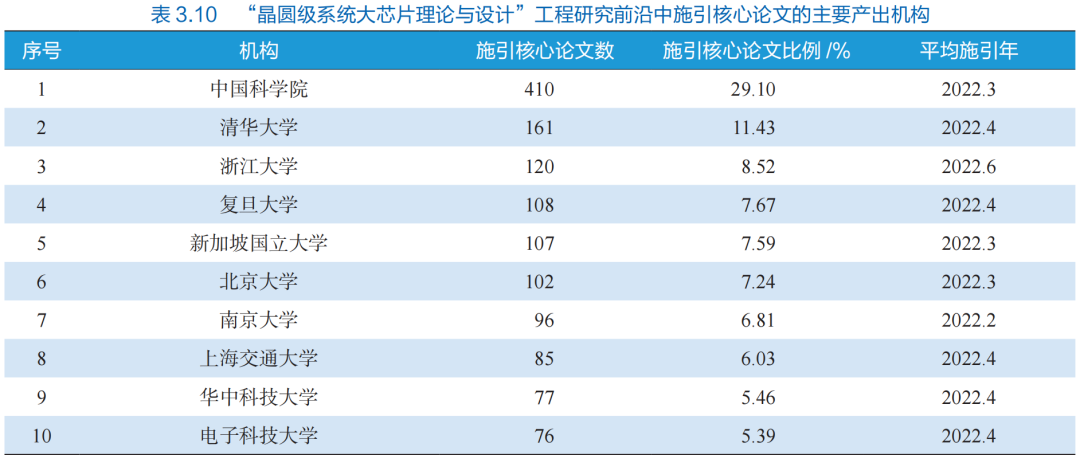

“晶圆级系统大芯片理论与设计”工程研究前沿中核心论文的主要产出国家见表3.7。美国的核心论文数排名第一,占比约为45%,论文平均出版年较早;中国仅次于美国,论文占比约为29%,处于快速追赶状态,平均出版时间较美国晚一年左右。中国与多个国家保持合作,欧洲的德国、英国、瑞士之间相互合作较为密切(图3.4)。在排名前十的核心论文产出机构中,5家来自美国,4家来自中国,1家来自韩国(表3.8)。在机构合作方面,除美国两家机构有合作关系外,其他机构之间鲜少合作(图3.5)。在施引核心论文方面,中国遥遥领先,施引核心论文数接近总数的一半,第二名是美国,其余国家的占比均低于10%(表3.9);在排名前十的施引核心论文产出机构中,除排名第五的新加坡国立大学外,其余均来自中国,体现了中国科研机构对该前沿的高度关注(表3.10)。

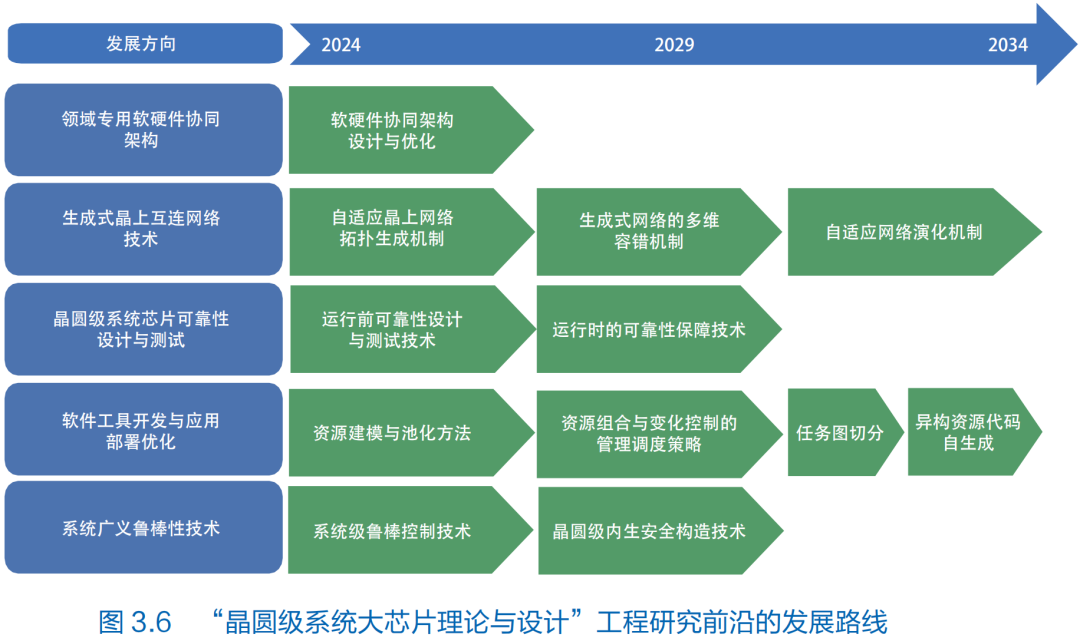

在过去5年中,晶圆级系统大芯片理论与设计取得了诸多研究成果。然而,从整个领域的发展进程看,其应用与研究仍处于起步阶段,存在众多亟待解决的瓶颈问题。该领域未来5~10年的重点发展方向(图3.6)如下:

1)领域专用软硬件协同架构。晶圆级系统大芯片具有计算/存储资源大规模、高密度集成,以及异构资源间低时延、大带宽传输能力等显著特征与优势,能够为适配不同应用的计算架构构建提供广阔的探索空间,但也给领域专用软硬件协同架构的设计和优化带来巨大挑战。

2)生成式晶上互连网络技术。高密度、强可塑的晶上互连网络对晶圆级系统芯片的功能、性能和效能至关重要。生成式晶上互连网络不仅要实现远超现有连接网络的高密度、大规模,还要实现高灵活和强可塑。因此,未来必须开展自适应晶上网络拓扑生成机制、生成式网络的多维容错机制、自适应网络演化机制等关键技术研究,以实现应用服务可软件定义,支撑晶圆级系统芯片的自演化。

3)晶圆级系统芯片可靠性设计与测试。由于高密度的集成架构和高动态的应用结构,晶圆级系统芯片在运行前的可靠性设计与测试及运行时的可靠性保障至关重要。未来研究方向包括晶圆级基板可靠性设计技术、跨尺度高精度高可靠集成技术、晶圆级高可靠供电散热技术、晶圆级可靠性测试与自调节技术等。

4)软件工具开发与应用部署优化。晶圆级系统大芯片大规模、高密度集成资源的多样化组合与应用任务的适配是NP难问题。为充分发挥晶圆级大芯片的优势,实现应用任务在晶圆级大芯片上的部署优化,未来研究重点包括:①晶圆级系统大芯片大规模、高密度集成资源建模与池化方法;②晶圆级系统大芯片支持资源组合和变化的管理调度策略;③充分利用晶圆级系统大芯片带宽优势实现任务图合理切分方法;④面向晶圆级系统大芯片异构资源的代码自动生成方法。

5)系统广义鲁棒性技术。随着面向不同领域应用晶圆级系统芯片的不断增多,不确定物理失效导致的系统鲁棒性问题、继承自异质异构芯粒的安全问题以及由分离制造导致的安全问题将更加严重,晶圆级系统芯片的广义鲁棒性控制技术也必然会引起更多关注。未来研究方向包括如何基于不可信芯粒从系统级构建安全架构并保持系统高性能。晶圆级系统安全芯片架构和硬件防御技术将成为研究重点,包括如何构建内生安全构造结构、如何在安全属性下进行软硬件协同优化等。

内容取自《全球工程前沿2024》

李沛杰,男,1990年出生,博士,山西襄汾人,信息工程大学助理研究员,主要研究方向为软件定义晶上系统、硬件安全、软件定义互连。(来源: 信息与电子工程前沿FITEE)

3.上海交大陈鹏课题组与许霄琰课题组在二维莫特绝缘体中发现量子自旋液体谱学证据

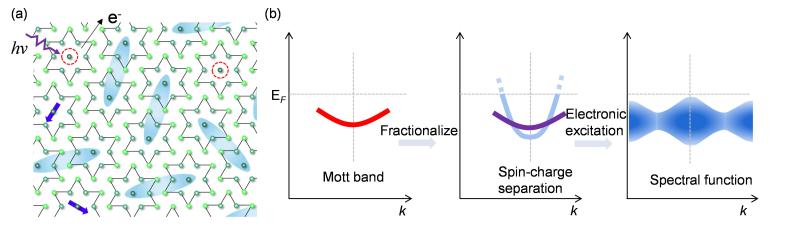

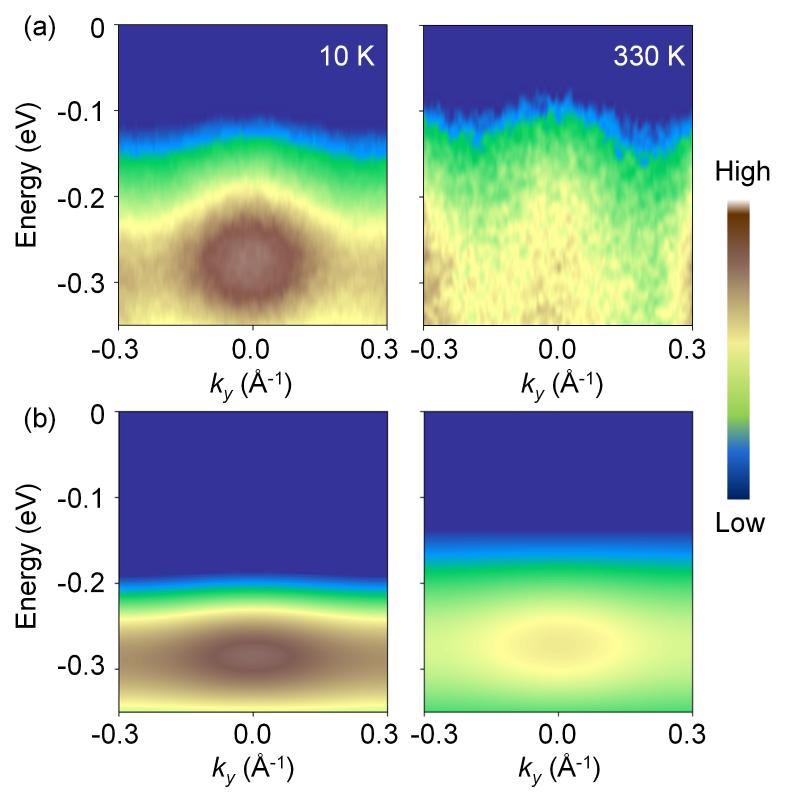

近日,上海交通大学物理与天文学院陈鹏课题组与许霄琰课题组在Physical Review Letters上发表了题为“Spectroscopic evidence for possible quantum spin liquid behavior in a two-dimensional Mott insulator”的研究论文,揭示了单层1T-TaS2中金属-绝缘体相变和量子自旋液体谱学行为。当具有局域化磁矩的莫特绝缘体中因量子涨落足够强而抑制自旋有序时,则会出现量子自旋液体态(Quantum Spin Liquid, QSL)。QSL具有奇异的量子特性:即自旋和电荷信息分离的集合激发—自旋子(spinon)和电荷子(chargon),这一直引发研究者的极大兴趣,但其证据主要局限于对自旋自由度的测量。理论上认为,QSL的电子态激发由自旋子和电荷子以及规范场耦合形成。在平均场近似下,自旋子和电荷子色散的卷积产生的电子能谱函数具有连续谱的特征,因而可以通过角分辨光电子能谱(Angle-resolved Photoemission Spectroscopy, ARPES)进行探测(图1)。

图1 量子自旋液体态电子分数化激发形成电子能谱示意图

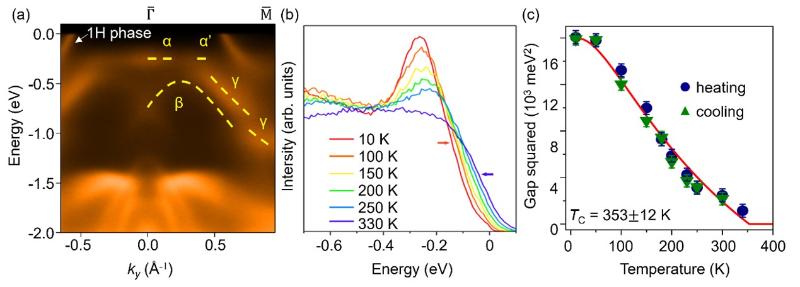

研究团队通过分子束外延法成功制备了高质量单层1T-TaS2薄膜,这种单层体系可以有效地排除层间耦合作用的影响。ARPES测量发现,在低温下单层1T-TaS2费米面附近出现平带,并且打开约260 meV的能隙,表明其绝缘性质。变温实验结果表明该能隙随温度升高而减小,拟合的相变温度(TC = 353 ± 12 K)是块体相变温度 (180 K) 的两倍,说明在二维 1T-TaS2中存在更稳定的莫特绝缘特性(图2)。费米面附近的平带表现出多个奇异特征:首先,尽管该平带在动量空间中几乎无色散(约10 meV),但其在点处半高宽约为0.2-0.3 eV,是其他能带的2-3倍;其次,随着动量的增加,该平带的谱权重迅速衰减,并在方向断开形成多个片段;最后,片段间隙随着温度升高增大,表明其起源并不是由电荷密度波打开的能隙。这种首次观察到的电子能谱特征与QSL低能有效模型给出的spinon-holon连续谱相符(图3)。

图2 (a)单层1T-TaS2的ARPES能谱,(b)和(c)能隙的温度依赖性和相变温度

由于电荷中性限制,1T-TaS2中预测的自旋子费米面难以被直接观测到,但可以通过磁性原子表面掺杂来研究。随着Fe或Co掺杂量的增加,平带的强度减弱,费米能附近的能隙逐渐关闭。能隙的减小表明在下Hubbard能带边缘附近存在填充能隙的态。这种掺杂效应并不能用化学势的刚性移动来描述,而是来自于游离的自旋子与磁性杂质的耦合,这种耦合形成自旋子近藤云,从而导致电荷重新分布。作为比较,非磁性杂质(如Na和K)的掺杂效应显示了完全相反的结果:不仅能隙进一步打开,平带强度也增加。分析表明,非磁性原子引起的化学势变化在掺杂中起到了主要作用。这些发现为从电子自由度的角度探索QSL证据开辟了新途径。

图3 单层1T-TaS2的ARPES能谱和低能有效模型模拟结果对比

上海交通大学物理与天文学院博士生陈海洋和王佛泓为论文的共同第一作者,陈鹏与许霄琰为共同通讯作者,高强,香港科技大学的高雪健博士和Kam Tuen Law教授为论文的合作作者,上海光源的陈振华与黄耀波研究员提供了基于同步辐射的光电子能谱支持。本工作主要由国家重点研发计划、国家自然科学基金、上海市科委、上海浦江计划,阳阳发展基金等项目的资助,在此深表感谢。 (来源: 上海交通大学)

4.北京理工大学在“超高强多层核壳纳米结构增强铝锂合金铸件”领域取得重要突破

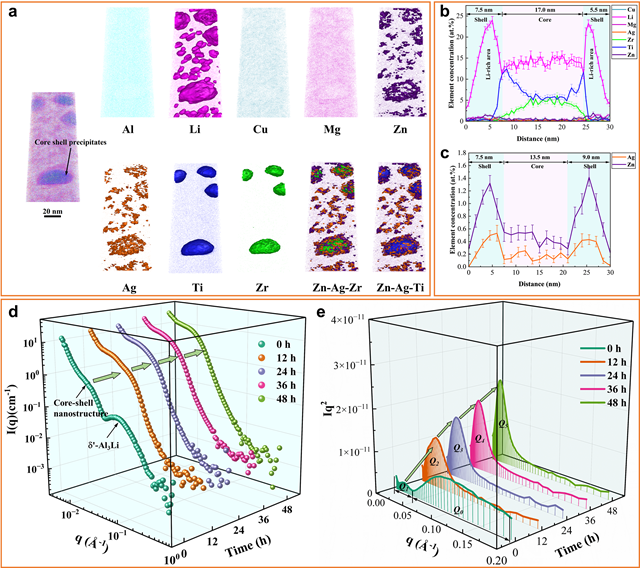

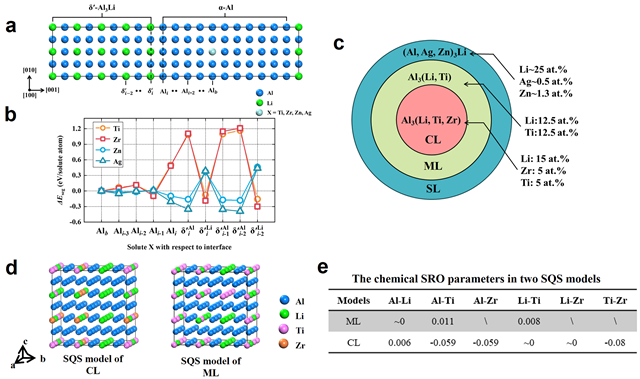

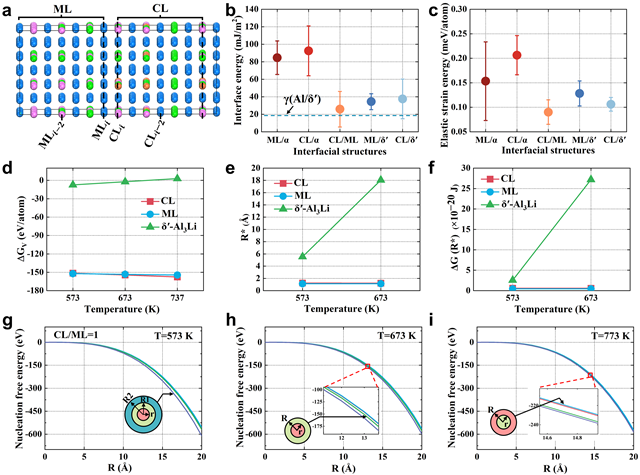

2月26日,北京理工大学材料学院博士生薛程鹏提出一种利用独特的多层核壳结构纳米析出相增强铝锂合金力学性能的策略,突破了传统铸造铝锂合金强度低的难题。研究发现了一种独特的富Li多层核壳结构纳米析出相,该析出相在时效态稳定存在且以高体积分数析出,通过沉淀强化使铸造铝锂合金的抗拉强度提升至接近500 MPa,可替代大部分变形铝锂合金。该研究成果以“An Ultrastrong Multilayer Core-Shell Nanostructure in Aluminum-Lithium Castings”为封面文章发表在国际顶级期刊Nano Letters上,北京理工大学博士研究生薛程鹏为本文第一作者,北京理工大学为唯一通讯单位,合作单位有中国散裂中子源(CSNS)、辽宁材料实验室(LAM)、和澳大利亚昆士兰大学等研究机构。

图1 铸造铝锂合金中超高强多层核壳结构析出相

铝锂合金由于加入较多轻元素Li,使其具有密度低(仅为其它铝合金的80%,钢、铜合金的1/3)、比强度比刚度高,已经在航空航天等获得大范围应用,但是变形加工价格昂贵、冷加工周期长造成其民用领域推广困难,比如低空飞行器减重、新能源汽车轻量化等。为了将航空航天用变形铝锂技术应用于低空经济、未来智能网联交通运输等领域,本文发明了工艺流程短、成本低的铸造铝锂合金,强度水平媲美传统变形铝锂合金。本研究提出了新型纳米析出相结构,解决了传统析出相的各种弊端,例如第二代铝锂合金强化相d¢-Al3Li不抗剪切缺点,以及塑性变形过程中共面滑移导致不均匀变形和晶界应力集中所致沿晶开裂和脆性问题;第三代铝锂合金强化相T1-Al2CuLi和θ′-Al2Cu相形核能垒高,晶界无析出带所致脆性断裂。同时,传统核壳结构析出相在铝锂合金中不能稳定存在,随着时效时间的延长则会转变为非核壳结构析出相,这种析出相结构转变降低铝锂合金力学性能。因此,本文发现的一种稳定的、低形核势垒的多层核壳结构共格纳米析出相为第四代铝锂合金研制另辟蹊径。

图2 多层核壳结构析出相的成分、结构剖析及其生长动力学的量化

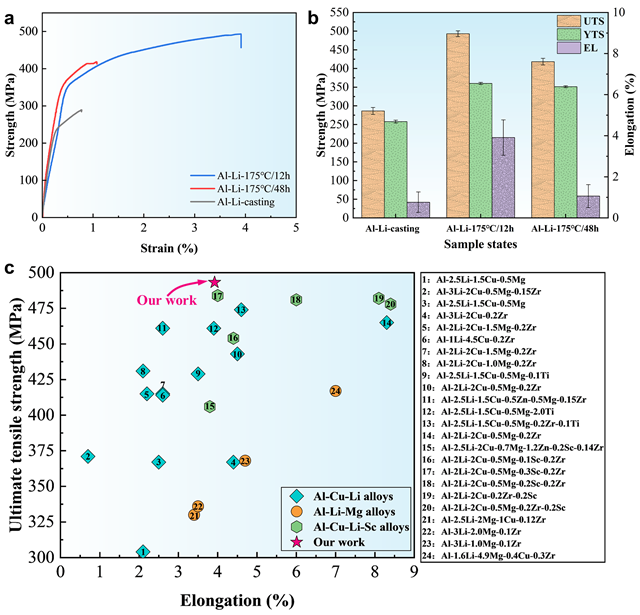

论文通过在Al-Li-Cu-Mg-Zn-Ti-Zr-Ag合金中控制不同Li、Cu含量,在175 ℃时效12 h形成了一种多层核壳结构析出相。通过HAADF-STEM、APT以及SANS多种表征手段揭示了其结构、成分和生长动力学,表明该析出相是以Al3Zr-Al3Ti作为核心层,富Ag-Zn作为中心层,Al3Li作为最外层的富Li多层核壳结构析出相,并且发现这种析出相生长动力学缓慢,具有极高的抗粗化能力以及高体积分数析出的优点,通过沉淀强化对屈服强度的贡献达到85%,最终使铸造的铝锂合金抗拉强度达到493.2 MPa。其强度超过了几乎所有以Al-Li-Cu、Al-Li-Mg和Al-Li-Cu-Sc为基础的铸造工程合金,奠定了适用于短流程、低成本新质生产力制造领域高强度轻质合金材料的基石。

图3 多层核壳结构析出相通过沉淀强化实现的铝锂合金力学性能与其它铝锂合金力学性能的对比

进一步地,研究团队基于DFT计算揭示了多层核壳结构的形成机制。利用 APT 表征的多层核壳结构析出相的化学成分,构建了它们各自的特殊准随机结构 (SQS) 超胞,通过偏析能计算确定的不同溶质原子 N (其中 N 代表 Zr、Ti、Ag 和 Zn)在 δ′/α-Al 界面附近的优先分布。发现Ti和Zr更倾向于占据δ′相中的Li的位点,而Ag和Zn则倾向于占据Al的位点。

图4 多层核壳结构析出相的原子占位、结构以及模型:(a,b)X(X = Zr、Ti、Ag和Zn)原子在共格(001)δ′/(001)α-Al界面占位的松弛原子模型以及相应的偏析能ΔEseg,右侧的灰色原子说明了X原子在α-Al的位点上的占据情况。在此,根据与界面平面的距离标注了晶格平面,(c)包含核心层(CL)、中间层(ML)和外壳层(SL)的多层核壳结构析出相示意图,以及各自的化学成分,(d,e)CL和ML部分的SQS模型,(e)SQS模型中组成原子的化学短程有序(SRO)参数的计算结果

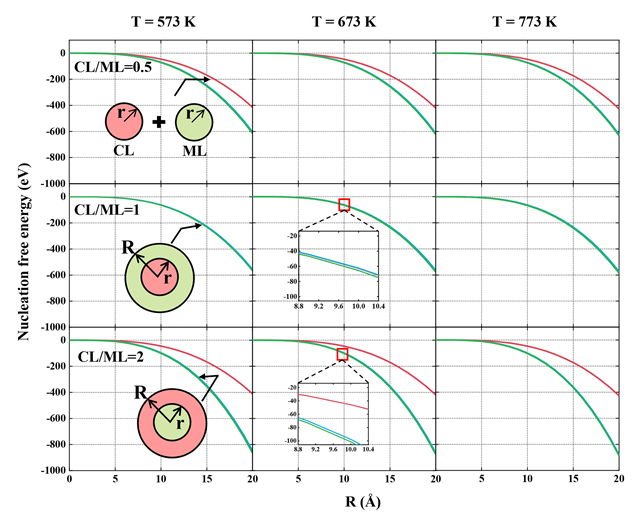

最后,研究团队基于DFT计算阐明了多层核壳结构的稳定机制。为了确定ML/α、CL/α、CL/ML、ML/δ′和CL/δ′中与连接相界面的局部原子无关的平均界面能和应变能,考虑了不同的界面终端。分析表明,CL/α的界面能超过ML/α,从而导致在铝合金中ML比CL优先析出。同样,CL/δ′的界面能略高于ML/δ′,这意味着ML可以润湿CL/δ′形成复合析出。值得注意的是,在所研究的界面结构中,与CL/ML界面相关的界面能和应变能都是最低的。因此,可以推断形成这种复杂的多层核壳结构是热力学上最有利的构型。δ′-Al3Li的临界形核半径(R*)在573 K时的预测值为5.54 Å,这一计算值接近与之前在相同温度下的4.14 Å,ΔGV(-7.33 meV/atom)的相应计算值也接近于-8.78 meV/atom。虽然与δ′相比,振动熵对CL和ML的ΔGV的影响较弱,但CL和ML相对于它们的共晶溶液的较大的ΔGV导致CL和ML的临界形核半径(R*)和临界形核功ΔG(R*)比δ′相的小得多,这或许可以解释CL和ML的性质以及由它们组成的多层核壳结构析出相。此外,图5(g-i)给出了在573 K、673 K和773 K三个典型时效温度下各种候选结构的形核自由能与析出半径的计算结果。最引人注目的发现是,无论温度(以ML和CL含量相等,即CL/ML = 1为例)和析出半径如何,四种候选结构的相对稳定性几乎都遵循相同的多层核壳结构排序:δ′/ML(CL)> ML(CL)> 分离的ML和CL > CL(ML)。事实上,对于不同的CL和ML含量比,计算结果也是一致的。当温度升高到773 K时,四种结构的形成能量几乎相同,这表明不同的结构可能共存。换句话说,对于尺寸小于2 nm的析出相来说,不存在占主导地位的结构类型。对于尺寸大于2 nm较大的大多数核壳结构析出相,多层核壳δ′/ML(CL)结构的形成能量要低得多。因此,在所有L12结构的析出相中,这种结构将占主导地位。

图5 不同核壳结构析出相的界面能、形成能、临界形核半径以及临界形核功的计算:(a)ML/CL的界面超胞示意图,考虑了不同界面终端的影响,(b,c)分别为(001)ML/(001)CL的立方体对立方体方向接触面的五个界面的界面能γ(mJ/m2)和共格应变能ΔGcs(meV/atom),(d-f)CL、ML和δ′相分别在不同温度下的体积形成能ΔGV(meV/atom)、临界形核半径R*(Å)和临界形核功ΔG(R*)(×10-20 J)的计算结果,(g-i)在不同析出温度下,核壳结构、多层核壳结构和分离结构的总形成能与析出半径的关系,紫色曲线表示多层核壳δ′/ML(CL)结构,绿色曲线表示核壳ML(CL)结构,红色曲线表示两个分离的ML和CL结构,蓝色曲线表示核壳CL(ML)结构。

图6 在不同的析出温度和CL/ML原子比下,核壳结构和分离结构的总形核自由能与析出半径的关系。红色曲线表示两个分离的ML和CL结构,绿色曲线表示核壳ML(CL)结构,蓝色曲线表示核壳CL(ML)结构

综上所述,研究团队提出了一种新型稳定强的多层核壳纳米结构析出相强化铝锂合金力学性能的策略,将铝锂合金加工成本、加工周期降低一半以上,力学性能提升将近2倍,满足未来交通对轻量化材料技术的需求。论文新发现的超强多层核壳结构析出相是一种独特的富Li、共格、纳米级单核双壳析出相(L12结构),这与之前报道的传统核壳结构不同,这种复杂的多层核壳结构既具有低错配诱导成核的优点,又具有在使用条件下高度稳定的特性。与传统的核壳结构相比,这种复杂的核壳结构具有最低的临界形核半径和自由能,使铸造的铝锂合金抗拉强度接近500 MPa。这种原创性调控思路为开发低成本、高性能铝锂合金指明了新的方向。(来源: 北京理工大学)

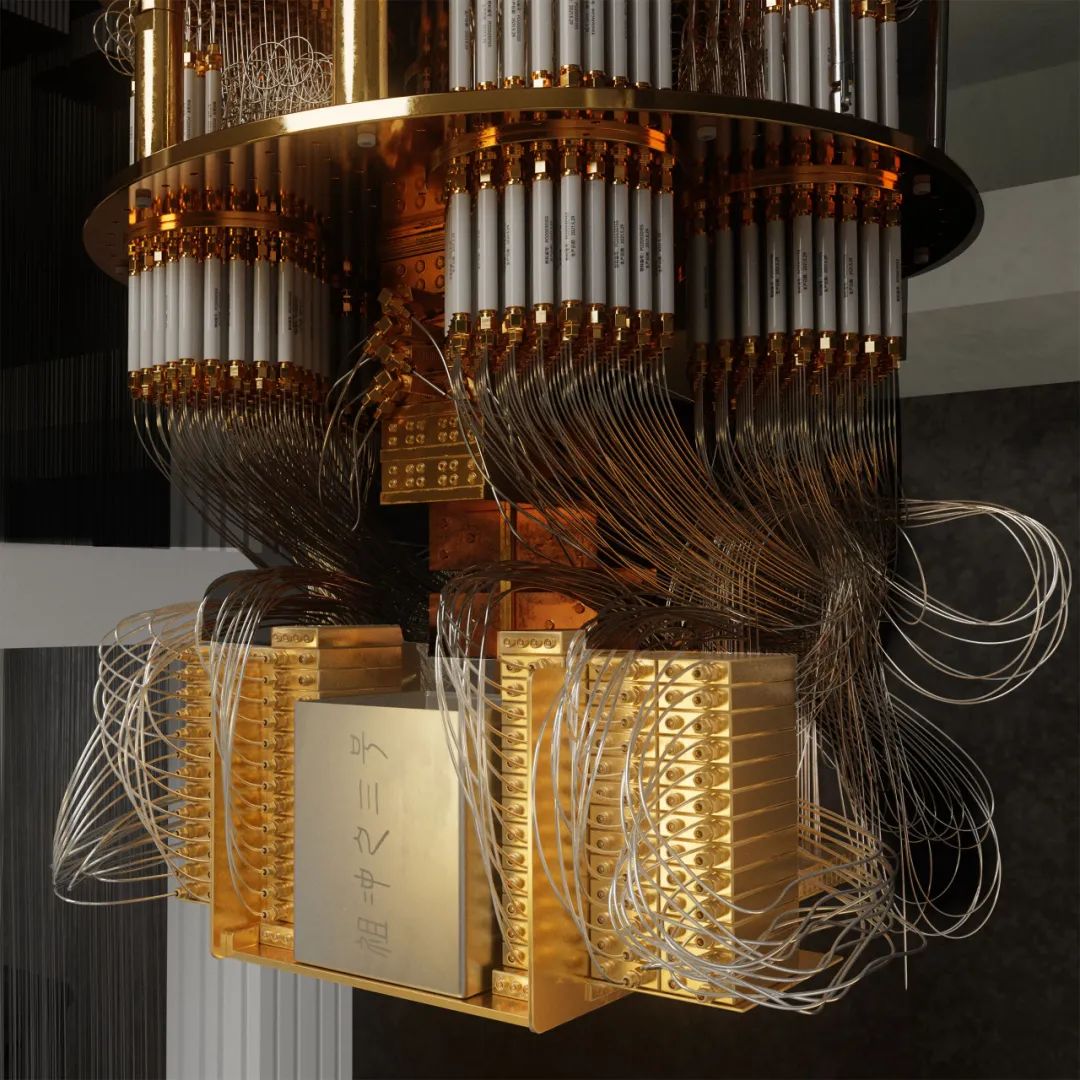

5.中国科学技术大学“祖冲之三号”创造新纪录 量子计算研究获新突破

中国科学技术大学潘建伟、朱晓波、彭承志等,与上海量子科学研究中心、河南省量子信息与量子密码重点实验室、中国计量科学研究院、济南量子技术研究院、西安电子科技大学微电子学院以及中国科学院理论物理研究所等单位合作,成功构建了105比特(包含105个可读取比特和182个耦合比特)超导量子计算原型机“祖冲之三号”,实现了对“量子随机线路采样”任务的快速求解。

与现有最优经典算法相比,“祖冲之三号”处理量子随机线路采样问题的速度,比目前最快的超级计算机快15个数量级,超过谷歌公司2024年10月公开发表的最新成果6个数量级。继超导量子计算原型机“祖冲之二号”后,再一次打破超导体系量子计算优越性纪录。

▲“祖冲之三号”芯片示意图。105个可读取比特和182个耦合比特集成在同一个芯片上执行量子随机线路采样任务。

量子计算优越性

国际竞争激烈

量子计算优越性验证了量子计算系统能够超越传统超级计算机的可行性,是量子计算研究实力的直接体现,也是量子计算具备应用价值的前提条件。

2019年,谷歌公司率先宣称实现量子计算优越性。谷歌公司53比特处理器在200秒内完成的随机线路采样任务,用当时最快的超级计算机进行模拟需要约一万年。

2023年,中国科学技术大学演示了更先进的经典算法,用1400余块A100 GPU仅需约14秒即可完成同样的任务。如果用“前沿”超算并配备更大的内存,则预计只需1.6秒即可完成。因此谷歌公司当时的“量子计算优越性”宣称已被中国科学技术大学推翻。

以最优经典算法为比较标准,中国科学技术大学于2020年实现国际上首个被严格证明的量子计算优越性。而超导体系首个被严格证明的量子计算优越性,同样由中国科学技术大学在2021年实现。

“祖冲之三号”

创造新纪录

研究团队在66比特“祖冲之二号”的基础上,大幅提升了各项关键性能指标。实现了105个数据比特、182个耦合比特的“祖冲之三号”, 量子比特相干时间达到72微秒,并行单比特门保真度达到99.90%,并行两比特门保真度达到99.62%,并行读取保真度达到99.13%,综合性能达到国际领先水平。

▲“祖冲之三号”。图片来源:中国科学技术大学“墨子沙龙”

为测试其性能,研究团队在“祖冲之三号” 系统上完成了83比特32层的随机线路采样,以目前最优经典算法为比较标准,为目前超导体系最强量子计算优越性。

相关成果于北京时间3月3日以封面论文的形式发表在国际学术期刊《物理评论快报》上。审稿人高度评价这一工作,认为其“构建了目前最高水准的超导量子计算机”“是对此前66比特处理器(祖冲之二号)的重大升级”。

目前研究团队正继续开展量子纠错、量子纠缠、量子模拟、量子化学等多方面探索,将为实现大规模量子比特的集成和操纵铺平道路。(来源: 中科院之声)