1、联电:暂无赴美设厂计划,专注与英特尔的合作项目

2、3D NAND闪存“卷”到1000层 可靠性挑战凸显

3、欧盟批准意大利13亿欧元补贴 助力Silicon Box建设先进半导体封装厂

4、日本Rapidus接收首台EUV光刻机 计划2027年量产2nm芯片

5、Micron上季度营收87.1亿美元,将继续扩大市场份额

6、英飞凌与亿纬锂能签约,将供应MCU等电池管理芯片方案

1、联电:暂无赴美设厂计划,专注与英特尔的合作项目

联电(UMC)近日表示,目前没有在美国设立生产基地计划,尽管有传言称该公司可能会面临在美国市场投资的压力。

有报道称,随着美国当选总统唐纳德·特朗普下个月将重返白宫,中国台湾第二大合约芯片制造商联电可能会面临更大的在美国投资的压力。消息人士称,这种压力可能是因为美国是全球最大的半导体市场,同时也由于特朗普的关税威胁。

联电对此表示,目前没有在美国投资的计划。该公司表示,目前正在集中资源与其美国芯片制造商英特尔公司(Intel Corp)合作正在进行中的项目。今年1月,联电和英特尔宣布将开发一个12nm半导体工艺平台。

英特尔位于亚利桑那州的奥科蒂洛技术制造基地的生产计划于2027年开始。

全球最大的合约芯片制造商台积电(TSMC)在亚利桑那州投资650亿美元,正在建设两个先进的晶圆厂,并计划再建一个。

根据市场信息咨询公司集邦科技(TrendForce Corp)的数据,联电在今年第三季度全球纯晶圆代工市场排名第四,仅次于台积电、韩国三星电子公司和中芯国际。

2、3D NAND闪存“卷”到1000层 可靠性挑战凸显

芯片行业正努力在未来几年内将3D NAND闪存的堆栈高度提高至四倍,从200层增加到800层或更多,利用额外的容量将有助于满足对各种类型内存的无休止需求。

这些额外的层将带来新的可靠性问题和一系列增量可靠性挑战,但近十年来,NAND闪存行业一直在稳步增加堆栈高度。2015年,东芝宣布推出首个使用硅通孔的16芯片堆栈,这实现了更高的带宽、更低的延迟和更快的I/O,同时也为堆叠其他类型的内存和逻辑芯片铺平了道路。

“最初,NAND是水平扩展的,”Lam Research(泛林集团)蚀刻生产力和设备情报副总裁Tae Won Kim表示,“但10多年前,制造商意识到横向扩展本身并不具有成本效益,因此他们转向了垂直扩展。”

堆叠芯片为显著提高密度和加快数据访问速度打开了大门。ACM Research(盛美半导体)总经理Mohan Bhan表示:“3D NAND的发展方向是500到1000层,但实现这么多层并非仅仅靠做更多我们一直在做的事情就能实现。”

主要的传统工艺问题与高纵横比(HAR)蚀刻和沉积有关,以确保所有这些层中的字符串一致且无空隙。由于多晶硅通道的总电阻增加,通道高度也对读取电流构成挑战。因此,一些开发人员正在转向使用混合键合的双晶圆解决方案,但这些改进只能到此为止。

Brewer Science业务发展经理Daniel Soden表示:“虽然尖端制造商始终致力于增加层数,但层的额外扩展/堆叠受到蚀刻预算和图案化挑战等因素的限制。”

但是达到1000层的最快的方法,也许是唯一的方法将是串堆叠。

业界提出增加内存容量的方法

业界确实有办法在不增加更多层的情况下增加内存容量。泛林集团的Kim表示:“NAND制造商不仅可以垂直扩展,还可以横向和逻辑扩展。”

逻辑缩放增加了单个闪存单元中存储的位数,而横向缩放则减少了单元之间的间距。此外,研究人员正在尝试将列一分为二,使单元总数增加一倍。各种想法都在发挥作用,但效果将是降低间距并在相同区域存储更多数据。“缩放这种电荷陷阱架构的间距是提高设备上电容器密度的好方法,而无需进一步增加层数。”Brewer的Soden说。

另一个容量提升的方法涉及将更多数据装入单个单元。在一个单元中存储多个位元并不是一个新想法。各公司正在推出每单元两位的多层单元(MLC)、三层单元(TLC)和四层单元(QLC)。开发人员现在正在接近每单元五层(五层单元或PLC)。管理如此微小的电荷状态差异(31个级别加上空)的算法可能会更复杂,纠错也是如此,因此性能可能会受到影响。

目前,PLC的实现方式以及陷阱氧化物的成分尚不明确,一些研究表明,浮栅可能成为更好的PLC单元。甚至有人在研究六层单元(HLC),每个单元存储六位。然而,这仍在研究中。

SK海力士有一种方法可以将存储单元分成两个三比特单元,总共六比特。七比特存储单元已经在低温下进行测试,以降低噪音并提高读取保真度。

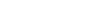

保持均匀的层次

堆叠3D NAND的基本优势在于,只需一个光刻步骤即可获得数百层,从而对所有层进行图案化。缺点是钻孔变得更加困难,尤其是当高深宽比接近100:1时。

让每层变薄似乎有利于增加层数,而不会使堆栈太高。“层厚度在150到100埃的范围内。”Bhan说。但字线层变薄会使它们的电阻变大,从而损害性能。一些研究人员正在探索用电阻更低的钌或钼代替钨金属。但对于产品开发来说,层厚度目前保持不变。

挑战不仅仅在于蚀刻,在保持良好平面度的同时添加额外的层更难。以前可以忽略的小错误现在累积起来,使得它们在更高的堆栈顶部变大而无法忽略。

堆栈最初由交替的SiO2和S3iN4层组成,但氮化物最终将被移除并替换为栅极金属。在每一代中,随着堆栈层数的增加,重点仍然是保持各层尽可能均匀。可以容忍轻微的错误,但随着堆栈层数的增加,这些错误往往会成倍增加,这意味着每一代都必须更加努力地提高平面度。

图1:3D NAND堆栈的平面性和均匀性较差。来源:盛美半导体

在沉积过程中旋转晶圆是盛美半导体用来提高平面度的一项技术。随着沉积的进行,该公司的设备会定期抬起晶圆并将其旋转180°,就像足球队每节改变方向一样。“沉积过程中对晶圆旋转的要求以及整个过程的均匀性将非常重要。”Bhan说。

为此,旋转卡盘将晶圆从压板上抬起,将其转动并放回原位。压板被加热,因此必须快速旋转以保持晶圆温度。但由于压板是固定的,因此晶圆在沉积过程中无法连续(缓慢)转动。“我们定期旋转晶圆以确保沉积更均匀,”Bhan解释说。“我们已经取得了相当大的进展,将均匀度控制在1%以内。”此外,该公司还控制沉积压力以补偿Si3N4中的拉应力和SiO2中的压应力。

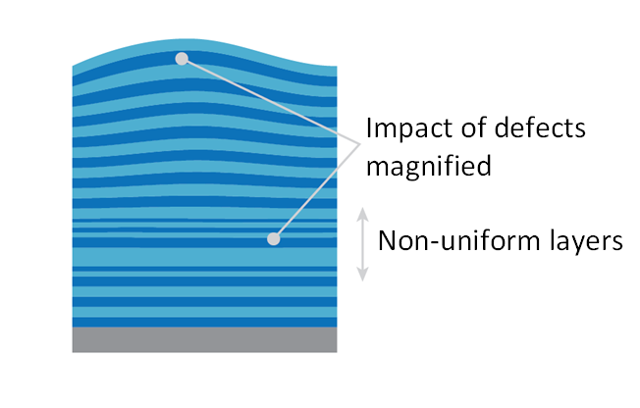

堆叠层数增加 潜在问题显现

随着堆栈层数的增加,潜在问题也随之增加。Brewer公司的Soden指出:“更高堆栈高度带来的物理和热应力会给光刻和其他下游工艺带来更多挑战。 ”

这在蚀刻过程中尤为明显。原本应该是笔直、均匀的柱状物,却可能因不同层上不同的横向蚀刻速率、顶部和底部之间的临界尺寸、蚀刻不完全,甚至柱状物偏离中心而变形。

图2:随着堆栈越来越高,蚀刻通道孔也会遇到越来越多的挑战。资料来源:盛美半导体

蚀刻工艺必须极其均匀,并且必须权衡利弊,以确保生产率不受影响。 “如果我们真的想同时实现纵向和横向微缩,我们不仅要提高蚀刻速率,还要改善轮廓控制,”泛林集团的Kim说道。

有效的蚀刻要求定义堆叠顶部图案的硬掩模保持良好的保真度。“正在研究更强大的图案转移解决方案,例如更厚的硬掩模和更具内在抗性的材料。”Soden说。目前使用的主要材料称为α碳(一种无定形碳),它非常坚硬。它是通过化学气相沉积(CVD)沉积的。”Brewer Science已经推出了一种它认为同样有效的材料,但它可以旋转,从而简化了流程。

“这种α碳的密度和硬度是其强项,可与钻石媲美,并且非常适合蚀刻工艺,”Soden说道。“用旋涂材料取代这种材料和工艺可以带来额外的灵活性、更高的产量、更好的间隙填充和其他特性,这些特性可以惠及我们行业的各种设备和领域。”

一旦蚀刻了柱状物,就必须对其进行清洁和干燥,这也变得更加困难。“一旦你完成了HAR蚀刻,让柱状物落到底部,就会有残留物。”盛美半导体首席技术专家Sally-Ann Henry说道,“问题是,柱状物的纵横比非常深。我们的超声波解决方案可以帮助将液体注入柱状物,但如何将液体排出呢?你可能可以将水注入和排出,但干燥是一个大问题。”

改进这些步骤的技术包括使用超声波搅拌将清洁材料推入圆柱体的每个角落,以及使用超临界 CO2在清洁后将其干燥。CO2的超临界阶段发生在高温和高压下,使材料具有气体和液体的性质。为了辅助,异丙醇既可以帮助在清洁前稳定图案,又可以在清洁完成后冲洗腔室。

单晶通道

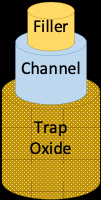

当完全构建并填充后,每个阵列列会形成所谓的Macaroni结构:同心排列,外部由陷阱氧化物组成,然后是通道材料,中间是惰性填充氧化物。陷阱氧化物是每个单元的电荷存储位置。通道成为位线或串,将电流一直传送到位线触点。填充部分的目的只是使通道变窄,从而改善栅极控制。

图3:3D NAND的Macaroni结构。电荷存储在陷阱氧化物中,通道形成位线。填充物的作用只是缩小通道以改善栅极控制。来源:Bryon Moyer/Semiconductor Engineering

通道本身通常是多晶硅,由于沿柱状结构存在许多晶粒边界,因此具有一定的电阻性。尽管它对于当前几代闪存来说效果很好,但随着堆栈越来越高,维持读取电流直至接触点变得越来越困难。出于这个原因,一些公司想出了生成单晶通道的方法。一种方法是从底部向上生长硅。另一种方法是从顶部结晶多晶硅。

应用材料公司指出,之前曾尝试使用选择性外延生长来创建单晶通道。但为了在加工过程中保护CMOS热预算,生长温度为810℃,导致生长速度太慢,无法进行批量生产。该公司可以在900至1100℃的温度下实现超过400nm/min的生长速度。虽然这可能会给传统的3D NAND加工带来问题,但一项新提出的技术可以实现这一点——在不同的晶圆上构建存储单元和逻辑并将它们混合键合在一起。

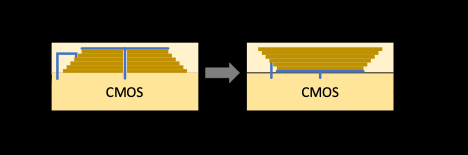

一种称为CMOS下方阵列(或CBA/CUA)的配置将单元阵列放置在一个晶圆上,将其余的CMOS电路放置在另一个晶圆上。两者使用混合键合结合在一起。由于键合的面对面性质,阵列和阶梯现在颠倒过来,并且接触可以短得多,这本身就是一个好处。

图4:阵列配置下方的CMO。单元结构构建在一个晶圆上,倒置,然后混合键合到包含CMO电路的晶圆上,缩短连接并允许阵列晶圆采用更高温度的工艺步骤。来源:Bryon Moyer/Semiconductor Engineering

但就外延生长而言,这允许阵列晶圆在高于CMOS所能承受的温度下生长外延,从而提供一种制造单晶通道的方法。然而,由此产生的一个变化是,由于通道占据了圆柱体的整个中部,填充氧化物消失了。这导致栅极控制减少,这是一个代价。改进的单晶通道性能需要产生更大的积极影响,才能使这种权衡值得。

双晶圆技术的成本也高得多。但它是独立于外延生长技术开发的,以便腾出阵列用于任何其他不利于CMOS的工艺。同样数量的闪存芯片也需要两倍的晶圆。这涉及到成本、晶圆需求和环境问题。

对于此应用,阵列载体晶圆中的硅不会被消耗。所有有用的层都沉积在该晶圆的顶部。将两个晶圆粘合后,典型的方法是研磨或蚀刻掉载体晶圆,这会浪费硅并增加成本。目前正在努力研究哪种技术可以修复回收晶圆的表面,使其与新晶圆一样有效。

自上而下的方法

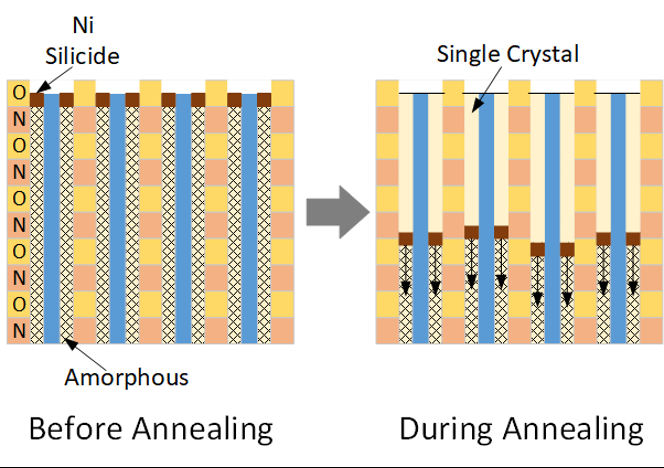

另一种创建这种通道的方法不需要两片晶圆。相反,通道中填充多晶硅,这是传统做法。然而,在退火之前,镍硅化物会沉积在通道上。在退火过程中,该硅化物会从顶部向下浮动,沿途催化结晶。当它到达底部时,其上方的所有东西都是单晶。硅化物仍留在底部,但位线触点位于顶部,因此不会造成问题(假设它留在原位)。

图 5:使用镍硅化物结晶通道。退火过程中,材料沿通道向下迁移,沿途结晶多晶硅。来源:Bryon Moyer/Semiconductor Engineering

堆叠并重复

最后,增加层数可以在一定程度上扭转在物理和地缘政治上处理越来越深的孔洞所取得的缓慢进展。上面讨论的改进有助于提高容量,但只能提高到一定程度。

“随着层数达到250以上,这些解决方案可能已接近极限,”Soden指出,“正在实施分步方法,将图案和蚀刻处理分解为不同的模块,以减少极端HAR蚀刻,在层之间引入裸硅并通过通孔方法进行连接。”

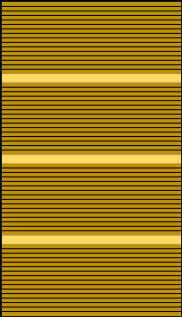

有时也被称为串堆叠,其理念是构建一组可管理的层,而不是试图使该堆叠更高,只需将堆叠彼此复制,并在每层堆叠之间添加一层硅即可。结果可以组合更多层,而不会出现所有扩展的HAR问题。“这种解决方案是推动许多公司长期推进多达1000层的原因,”Soden说。

图6:串堆叠。每组层都独立地经过正常过程。堆叠独立的串可以实现更多层,而无需在一个步骤中处理整个堆栈。代价是需要多个步骤。来源:Bryon Moyer/Semiconductor Engineering

工程解决方案是,人们可以得到1000层,而不必将它们一起处理。相反,人们可以处理250层,然后堆叠四个模块,中间插入硅层。代价是需要四个光刻步骤,而不是一个,但这可能是一个合适的权衡。似乎没有人讨论尝试以传统的方式处理1000层。

这并不像听起来那么简单,因为第二层将放置在第一层之上,而不是放置在一块平坦的晶圆之上。第三层必须在第二层上积累的任何不规则之处之上工作。很可能每一层都需要单独的开发工作来确保足够的平面度。

另一个挑战是,每层中的串必须以某种方式连接起来才能形成一个长串。简单的答案是在硅隔离层中放置一个通孔,但将每一层与前一层精确对齐并不明显——因为硅层会阻挡下面列的可见性。

从地缘政治角度来看,出口规则限制堆叠层数超过128层。因此,受这些限制的国家只需堆叠128层模块即可绕过这一限制。

需要几年时间才能解决这个问题

NAND闪存的改进涉及许多活动部件。改进HAR处理的努力将继续,但这并不是最大的收获。理论上,PLC技术可立即提高25%的容量。单元架构的改变和间距的减小可以带来更多帮助。

最大的变化是转向双晶圆解决方案和堆叠串的重大架构转变。它们可以与其他容量提升一起出现。采用这两种技术的产品目前都有,尽管不是1000层。降低CBA成本是实现普及的必要条件,而且需要努力扩展堆叠层的数量。

目前主流配置究竟是什么样子还不清楚,但无论如何,更大容量的NAND闪存芯片将满足业界对于存储的无尽需求。

参考链接:https://semiengineering.com/nand-flash-targets-1000-layers/

3、欧盟批准意大利13亿欧元补贴 助力Silicon Box建设先进半导体封装厂

根据欧盟国家援助规则,欧盟委员会批准了一项13亿欧元的意大利补贴,以支持新加坡初创公司Silicon Box在诺瓦拉建造一个半导体先进封装和测试设施。

意大利通知欧盟委员会,其计划支持Silicon Box在意大利诺瓦拉建立新的半导体先进封装和测试设施的项目。先进封装允许将多个通常具有不同功能的芯片集成到一个封装中,从而创建一个多芯片模块或“chiplet(小芯片)”。这种方法使chiplet能够像单个芯片一样运行,从而提供更好的性能和功率效率。

新工厂将提供先进的封装解决方案,使用面板级而不是晶圆级封装以及3D集成技术集成小芯片。该工厂将处理关键的制造步骤,即芯片组装、封装和测试。该工厂预计将于2033年满负荷运行,预计每周可处理约10000块面板。

援助将以向Silicon Box直接拨款约13亿欧元的形式提供,以支持其总价值32亿欧元的投资。根据该措施,Silicon Box同意为欧盟下一代先进封装技术的发展做出贡献,并根据《欧洲芯片法》,在供应短缺的情况下执行优先订单。Silicon Box还表示将开发和部署教育和技能培训,以增加合格和熟练的劳动力队伍。

Silicon Box的项目将成为欧洲首个提供面板级先进封装解决方案的先进封装设施。

2024年4月,意大利企业和意大利制造部长阿道夫·乌尔索(Adolfo Urso)宣布,Silicon Box计划投资32亿欧元在意大利新建一座半导体工厂。2024年初,Silicon Box宣布已筹集到价值2亿美元的资金,尽管尚未在任何证券交易所上市,但总估值已超过10亿美元。

Silicon Box在意大利的投资将于今年完成,该项目将通过建立灵活的全球半导体芯片供应链,提高全球半导体制造能力。预计前十五年的运营成本将超过40亿欧元。

4、日本Rapidus接收首台EUV光刻机 计划2027年量产2nm芯片

Rapidus已开始在其位于北海道北部城市千岁的在建芯片制造设施中安装极紫外(EUV)设备,这使其成为首家接收EUV光刻设备的日本半导体公司。

“我们将从北海道和日本向全世界提供尖端半导体,”Rapidus CEO小池淳义于新千岁机场举行的仪式上表示。

由荷兰供应商ASML制造的首批EUV光刻系统部件于上周六抵达机场,预计该系统在工厂的安装将在本月底完成。

由于系统体积巨大,安装将分四个阶段进行。一个完整的设备重达71吨,大约与鲸鱼相当,高度为3.4米。

EUV设备结合了特殊光源、镜头和其他技术,以形成超精细的电路图案。系统的庞大体积使其不易受到振动和其他干扰的影响。

ASML是全球唯一的EUV系统供应商。每个系统的成本约为1.8亿美元或更高。只有少数芯片制造商采用了它们,包括台积电、三星电子和英特尔。去年全球仅交付了42套系统。

Rapidus正与IBM合作,计划在2025年春季开发使用尖端2nm工艺的原型芯片,并计划在2027年大规模生产这些芯片。台积电计划在2025年大规模生产2nm芯片。

日本半导体产业在1980年代曾占据全球市场份额的50%以上。但到了2000年代,日本退出了生产越来越小的逻辑芯片的竞争。

目前没有日本芯片制造商能够生产比40纳米更先进的芯片。

5、Micron上季度营收87.1亿美元,将继续扩大市场份额

2024年12月18日,Micron公布了截至2024年11月28日的2025财年第一季度业绩。

据报告,Micron第一季度营收87.1亿美元,上一季度为77.5亿美元,去年同期为47.3亿美元;数据中心营收环比增长超40%,同比增长超400%;运营费用为11.7亿美元,上一季度为12.2亿美元;净利润为18.7亿美元,摊薄后每股收益1.67美元;运营现金流为32.4亿美元,上一季度为34.1亿美元,去年同期为14.0亿美元。

“美光实现了创纪录的季度业绩,我们的数据中心收入首次超过了总收入的50%,”Micron总裁兼首席执行官Sanjay Mehrotra表示,“虽然面向消费者的市场在短期内表现疲软,但我们预计本财年下半年将恢复增长。我们将继续在利润率最高且具有重要战略意义的市场领域扩大份额,并将利用人工智能驱动的增长为所有利益相关者创造巨大价值。”

对于2025财年第二季度,Micron预计营收将在77亿至81亿美元之间,毛利率将在36.5%至38.5%之间,运营费用将在12.25亿至12.55亿美元之间,摊薄后每股收益将在1.16至1.36亿美元之间。

6、英飞凌与亿纬锂能签约,将供应MCU等电池管理芯片方案

12月18日,英飞凌发文称,英飞凌与锂电池制造商亿纬锂能签署合作备忘录(MoU)。双方将共同为汽车市场提供综合的电池管理系统解决方案。

根据合作备忘录,英飞凌将提供整套芯片解决方案,包括微控制单元(MCU)、电池均衡和监测IC、电源管理IC、驱动、MOSFET、CAN和传感器产品。通过采用这些解决方案,亿纬锂能的电池管理系统将拥有高度的安全性、可靠性以及更加优化的成本,而且能够更加准确地监测、保护和优化电动汽车(EV)的电池性能,提升用户的驾驶体验和车辆的能效。

英飞凌科技高级副总裁兼智能电源产品线总经理Andreas Doll表示,电气化的快速发展推动了对先进电池解决方案的需求。英飞凌领先的电池管理IC与亿纬锂能先进的电池技术将共同为下一代智能电池组奠定基础。英飞凌通过提供全面而先进的系统级解决方案,满足了客户的不同需求。相信双方的进一步合作将促进各个层面的良性互动和协同发展。