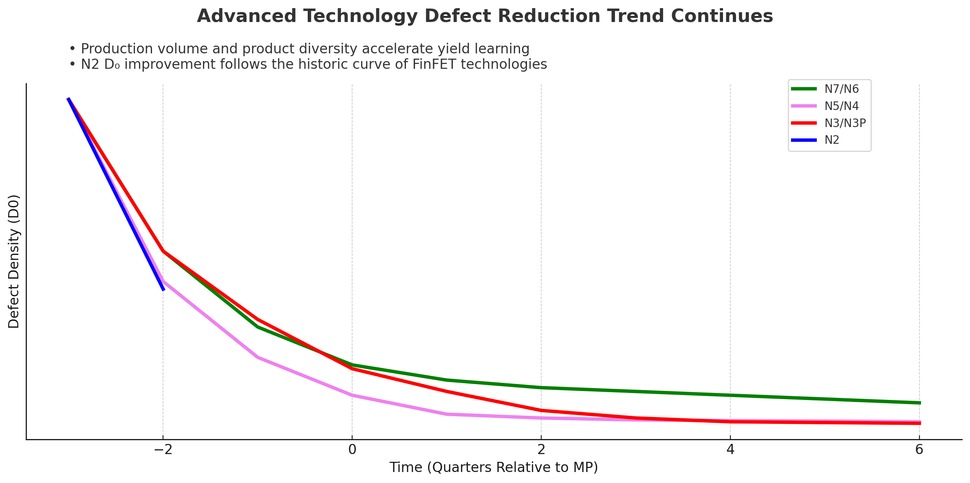

台积电近期在北美技术研讨会上公布了其N2(2nm)工艺技术相对于同阶段前代工艺的缺陷密度(D0)。据该公司称,N2工艺的缺陷密度低于N3(3nm)、N5(5nm)和N7(7nm)制造节点。此外,幻灯片显示,台积电N2工艺距离量产还有两个季度,这意味着台积电有望按预期在2025年第四季度末开始生产2nm芯片。

尽管台积电的N2工艺是该公司首个采用全栅环(GAA)纳米片晶体管的工艺技术,但该节点的缺陷密度低于同阶段的前代工艺,比量产(MP)提前两个季度。前代工艺——N3/N3P、N5/N4和N7/N6——都采用了成熟的鳍式场效应晶体管(FinFET)。因此,尽管N2是台积电首个采用GAA纳米片晶体管的节点,但其缺陷密度下降幅度比前代工艺在进入大规模生产(HVM)里程碑前更大。

该图表绘制了缺陷密度随时间的变化,时间跨度从量产前的三个季度到量产后的六个季度。在所有显示的节点中——N7/N6(绿色)、N5/N4(紫色)、N3/N3P(红色)和N2(蓝色),缺陷密度随着产量提升而显著下降,但下降速度因节点复杂度而异。值得注意的是,N5/N4在早期缺陷减少方面最为积极,而N7/N6的良率提升则较为平缓。N2曲线的初始缺陷水平高于N5/N4,但随后急剧下降,与N3/N3P的缺陷减少轨迹非常接近。

幻灯片强调,产量和产品多样性仍然是加速缺陷密度改进的关键驱动因素。更大的产量和使用相同工艺的多样化产品能够更快地识别和纠正缺陷密度和良率问题,从而使台积电能够优化缺陷学习周期。台积电表示,其N2制造技术比前代技术获得了更多新的流片(因为台积电现在为智能手机和高性能计算(HPC)客户风险生产N2芯片),缺陷密度下降曲线基本证实了这一点。

考虑到引入全新晶体管架构所带来的风险因素,N2的缺陷减少率与之前基于FinFET的节点保持一致,这一点尤为重要。这表明台积电已成功将其工艺学习和缺陷管理专业知识转移到新的GAAFET时代,且未遭遇重大挫折。(校对/李梅)