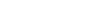

从今天开始,我们聊聊芯片的封装和测试(通常简称“封测” )。

这一部分,在行业里也被称为后道( Back End)工序,一般都是由OSAT封测厂(Outsourced Semiconductor Assembly and Test,外包半导体封装与测试)负责。

封装的目的

先说封装。

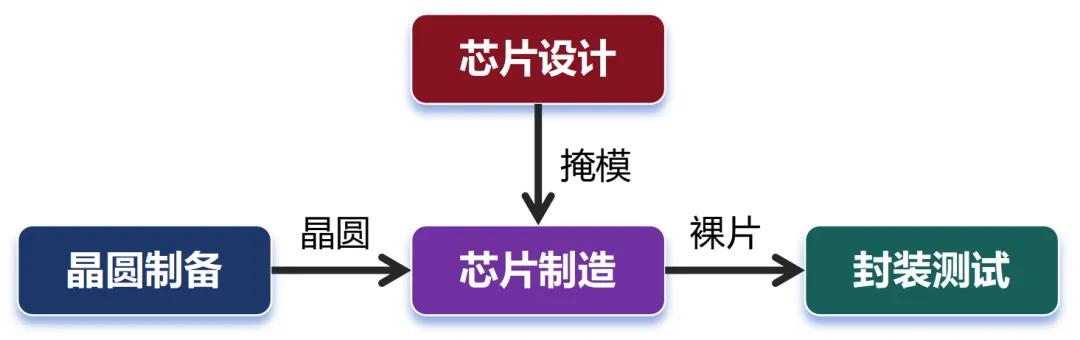

封装这个词,其实我们经常会听到。它主要是指把晶圆上的裸芯片(晶粒)变成最终成品芯片的过程。

之所以要做封装,主要目的有两个。

一个是对脆弱的晶粒进行保护,防止物理磕碰损伤,也防止 空气中的杂质 腐蚀晶粒的电路。

二是让芯片更适应使用场景的要求。

芯片有很多的应用场景。不同的场景,对芯片的外型有不同的要求。进行合适的封装,能够让芯片更好地工作。

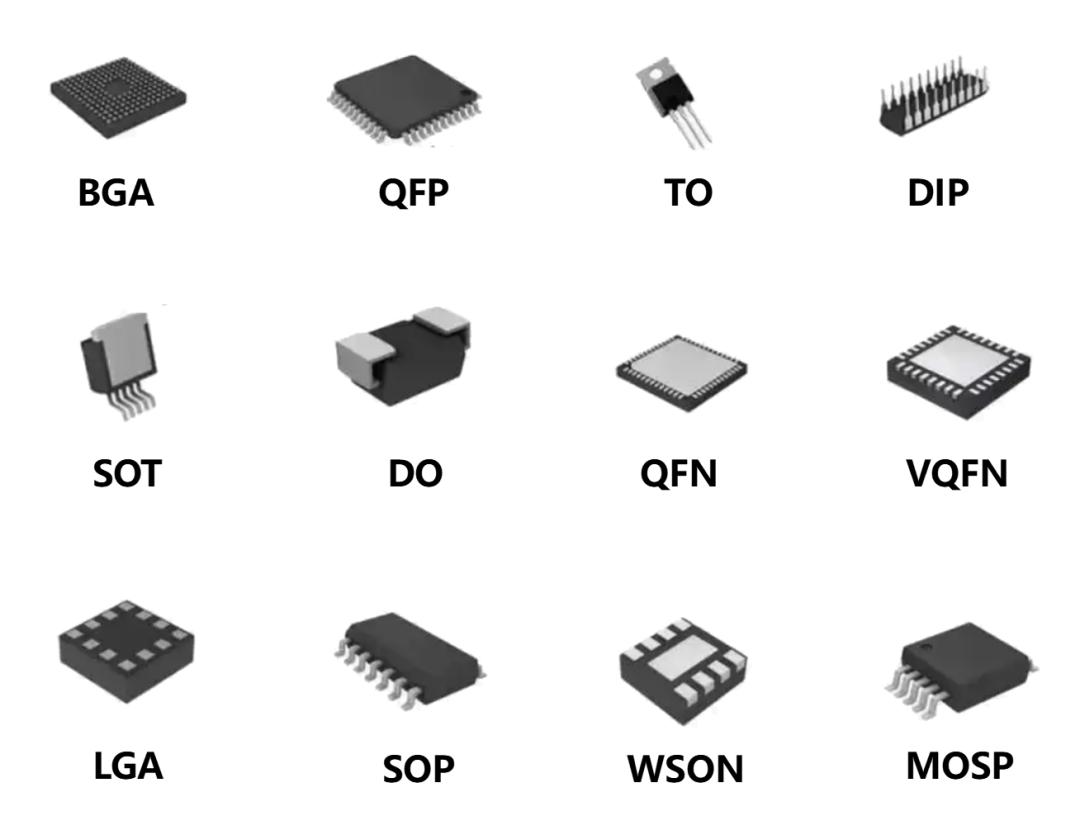

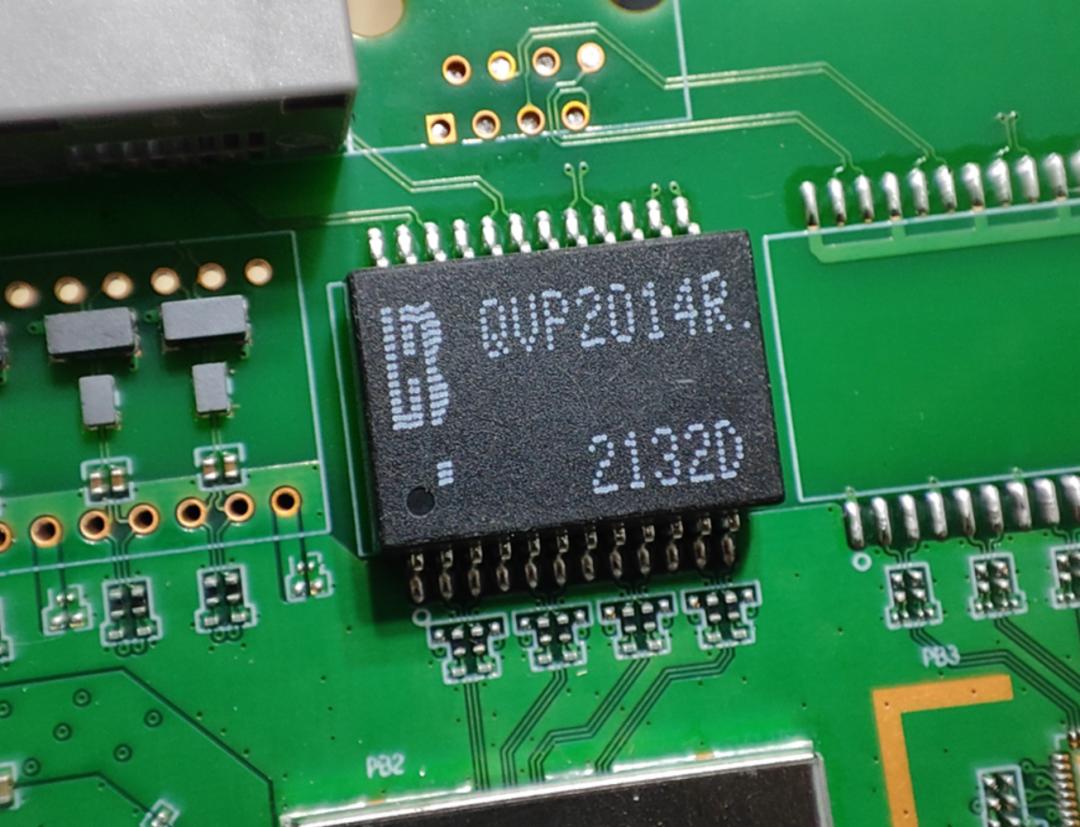

我们平时会看到很多种外型的芯片,其实就是不同的封装类型

封装的发展阶段

封装工艺伴随芯片的出现而出现,迄今为止已有70多年的历史。

总的来看,封装工艺一共经历了五个发展阶段:

接下来,我们一个个来说。

传统封装

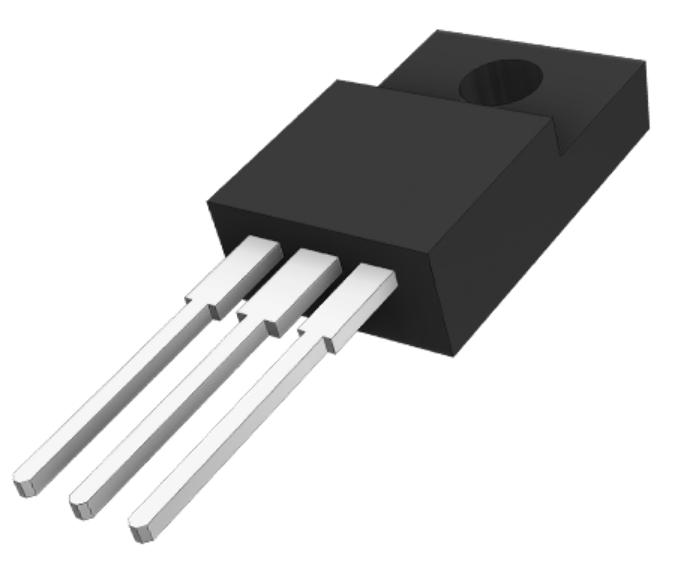

最早期的晶体管,采用的是TO(晶体管封装)。后来,发展出了DIP( 双列直插封装)。

我们最熟悉的三极管造型,就是TO封装

再后来, 由PHILIP公司开发出了SOP(小外型 封装 ),并逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

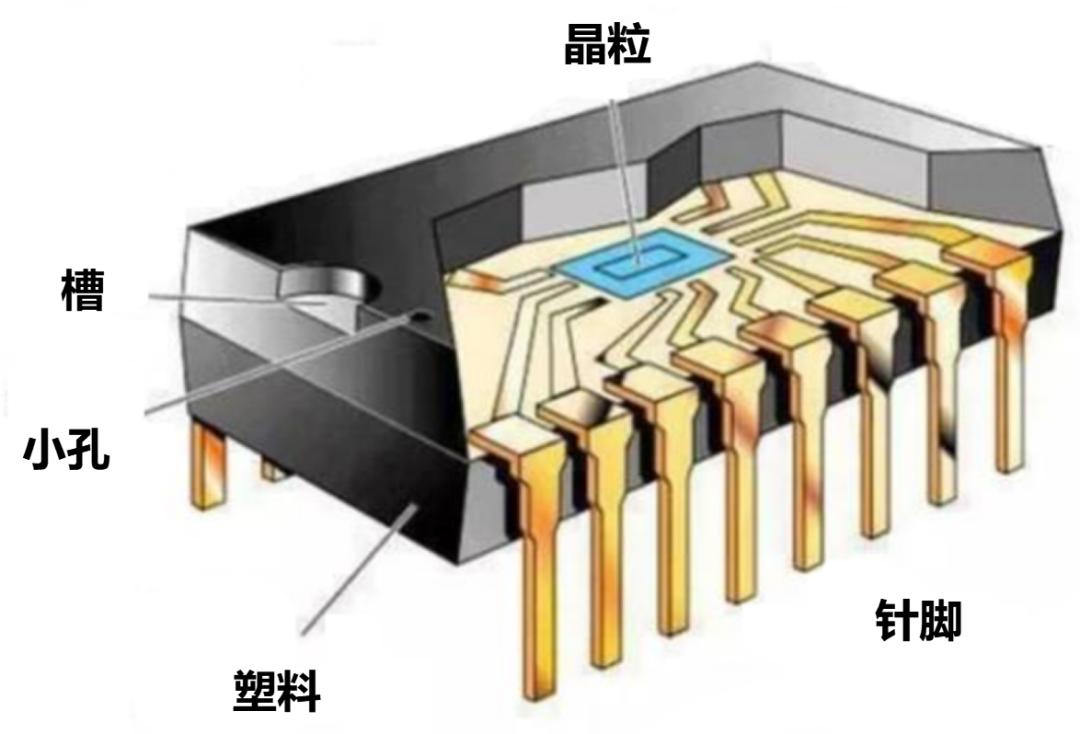

DIP内部构造

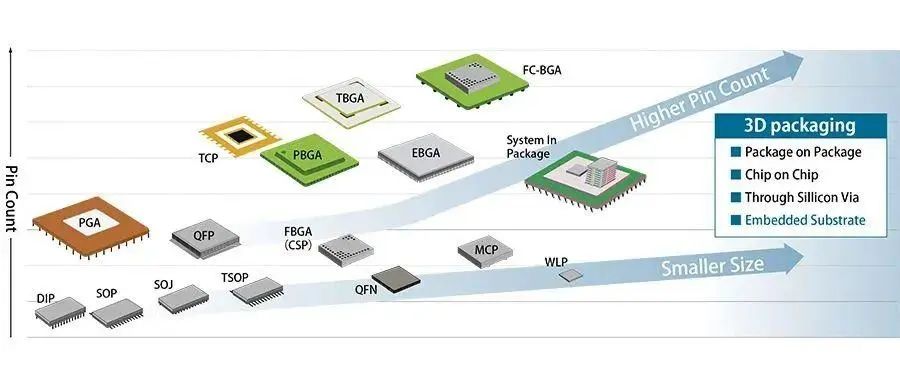

第一、第二阶段(1960-1990年)的封装,以通孔插装类封装(THP)以及表面贴装类封装(SMP)为主, 属于传统封装。

传统封装,主要依靠引线将晶粒与外界建立电气连接。

这些传统封装,直到现在仍比较常见。尤其是一些老的经典型号芯片,对性能和体积要求不高,仍会采用这种低成本的封装方式。

第三阶段(1990-2000年),IT技术革命加速普及,芯片功能越来越复杂,需要更多的针脚。电子产品小型化,又要求芯片的体积继续缩小。

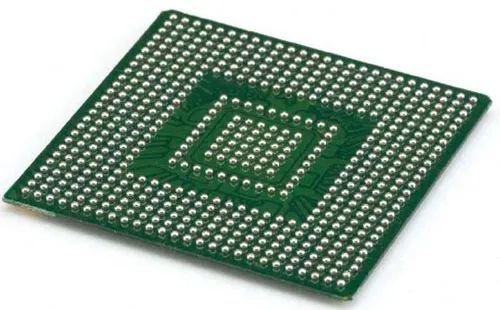

这时, BGA( 球型矩阵、 球栅阵列) 封装开始出现,并成为主流。

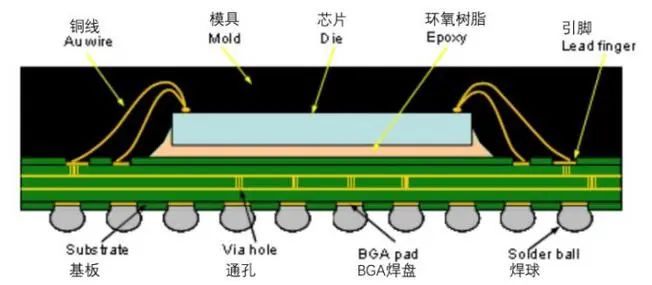

BGA仍属于传统封装。它的接脚位于芯片下方,数量庞大,非常适合需要大量接点的芯片。而且,相比DIP,BGA的体积更为紧凑,非常适合需要小型化设备。

BGA封装

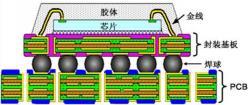

BGA封装内部

和BGA有些类似的,还有LGA(平面网格阵列封装 )和PGA( 插针网格阵列封装)。大家应该注意到了,我们最熟悉的CPU,就是这三种封装。

先进封装

20世纪末,芯片级封装( CSP)、晶圆级封装(WLP)、 倒装封装 (Flip Chip )开始慢慢崛起。传统封装开始向先进封装演变。

相比于BGA这样的封装, 芯片级封装( CSP)强调的是尺寸的更小型化(封装面积不超过芯片面积的1.2倍)。

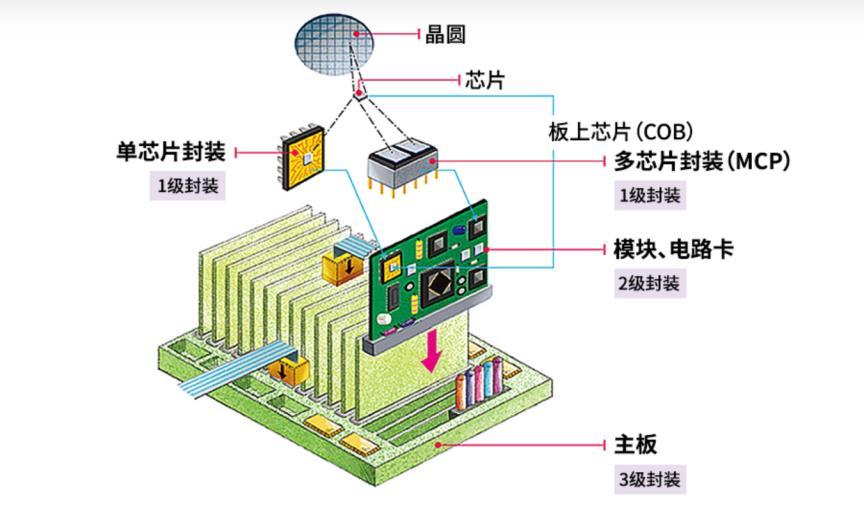

封装的层级(来自 Skhynix)

晶圆级封装是芯片级封装的一种,封装的尺寸接近裸芯片大小。

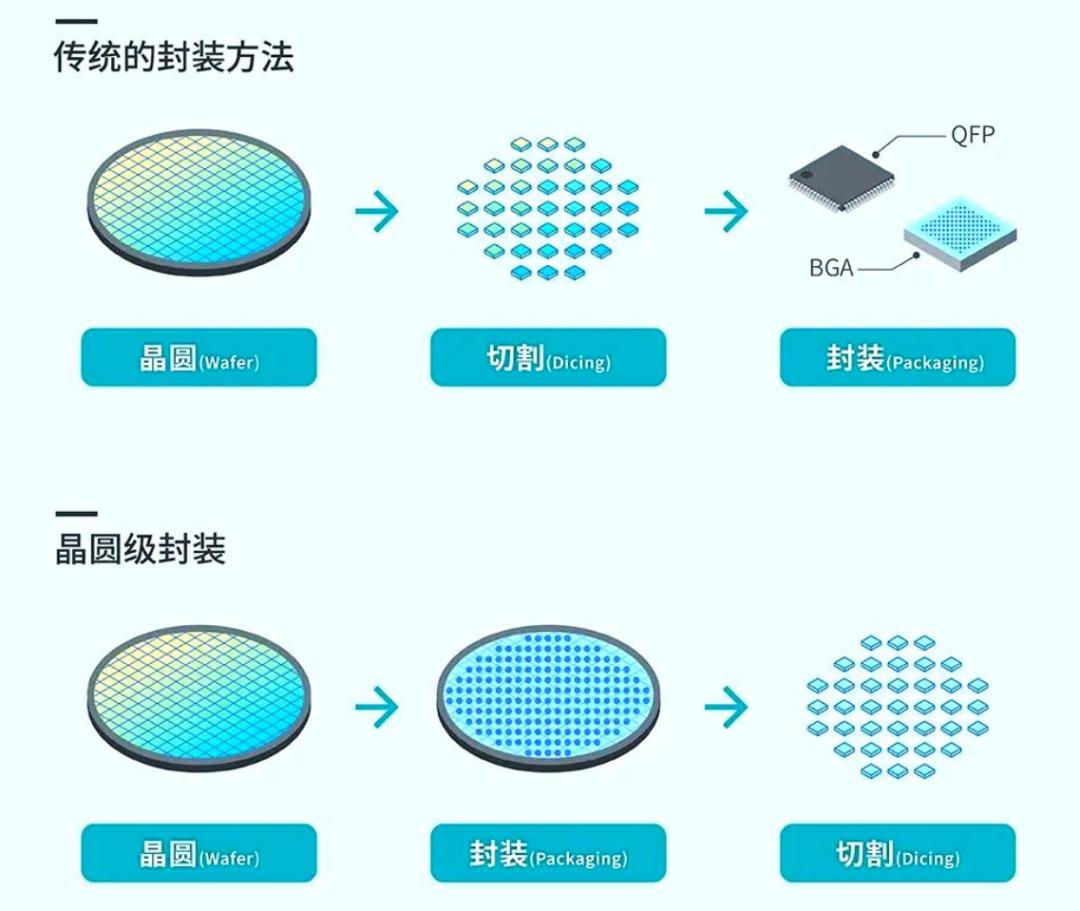

下期我们讲具体工艺的时候,会提到封装包括了一个切割工艺。 传统封装,是先切割晶圆,再封装。而晶圆级封装,是先封装,再切割晶圆,流程不一样。

晶圆级封装

倒装封装 (Flip Chip )的发明时间很早。1960年代的时候,IBM就发明了这个技术。但是直到1990年代,这个技术才开始普及。

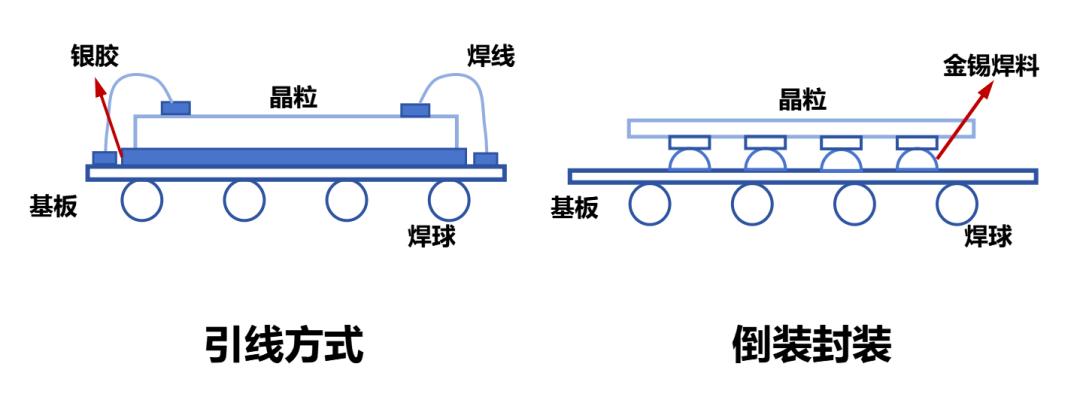

采用倒装封装,就是不再用金属线进行连接,而是把晶圆直接反过来,通过晶圆上的凸点( Bump),与基板进行电气连接。

和传统金属线方式相比,倒装封装的I/O(输入/输出)通道数更多,互连长度缩短,电性能更好。另外,在散热和封装尺寸方面,倒装封装也有优势。

先进封装的出现,迎合了当时时代发展的需求。

它采用先进的设计和工艺,对芯片进行封装级重构,带来了更多的引脚数量、更小的体积、更高的系统集成度, 能够大幅提升系统的性能。

进入21世纪后,随着移动通信和互联网革命的进一步爆发,促进芯片封装进一步朝着高性能、 小型化、低成本、高可靠性等方向发展。先进封装技术开始进入高速发展的阶段。

这一时期,芯片内部布局开始从二维向三维空间发展(将多个晶粒塞在一起),陆续出现了 2.5D/3D封装、 硅通孔(TSV)、重布线层(RDL)、扇入(Fan-In)/扇出(Fan-Out)型晶圆级封装、系统级封装(SiP)等先进技术。

当芯片制程发展逐渐触及摩尔定律的底线时,这些先进的封装技术,就成了延续摩尔定律的“救命稻草”。

先进封装的关键技术

2.5D/3D封装

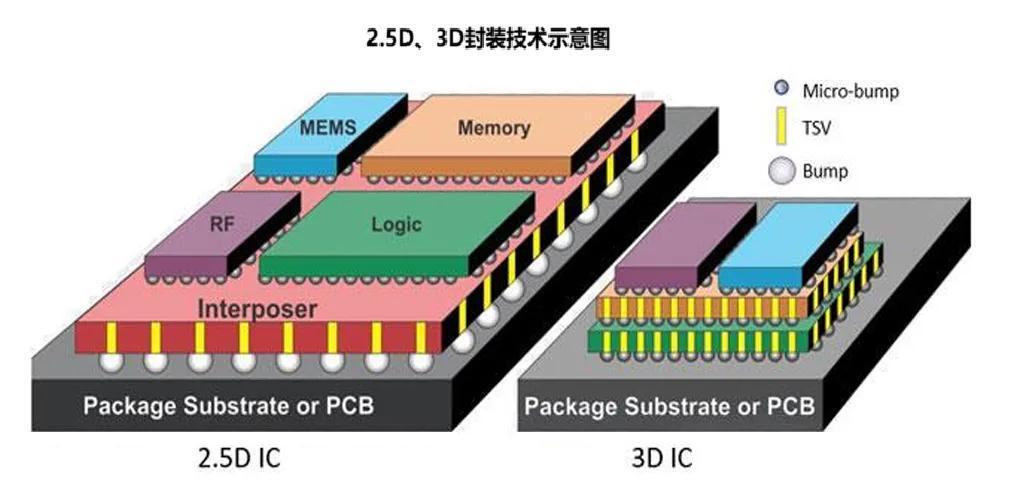

2.5D和3D封装,都是对 芯片进行堆叠封装。

2.5D封装技术,可以将两种或更多类型的芯片放入单个封装,同时让信号横向传送,这样可以提升封装的尺寸和性能。

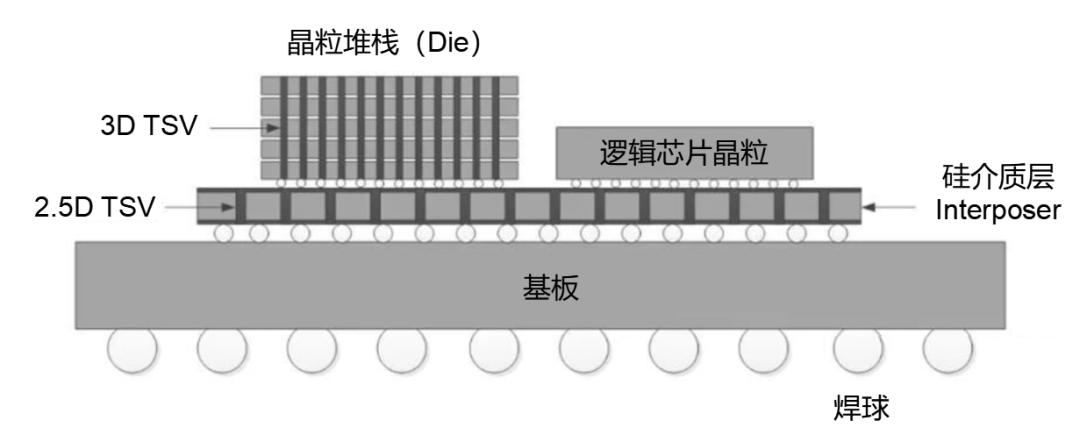

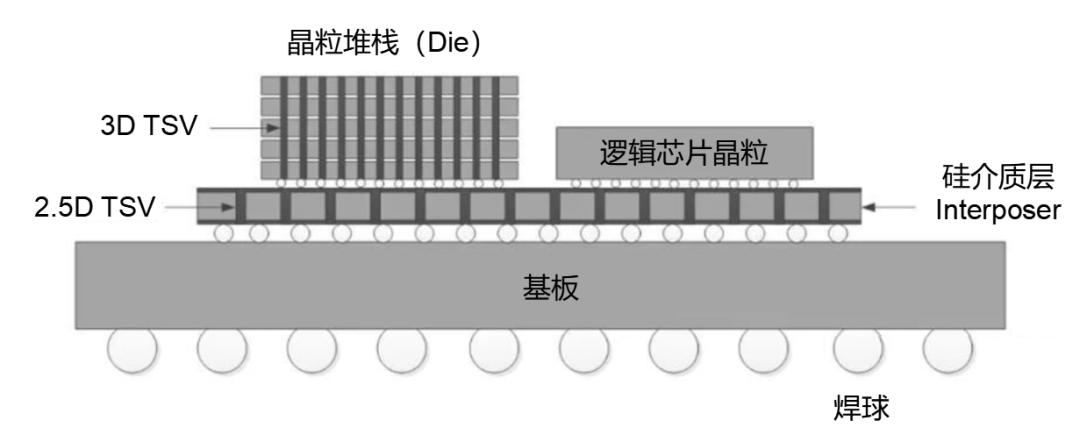

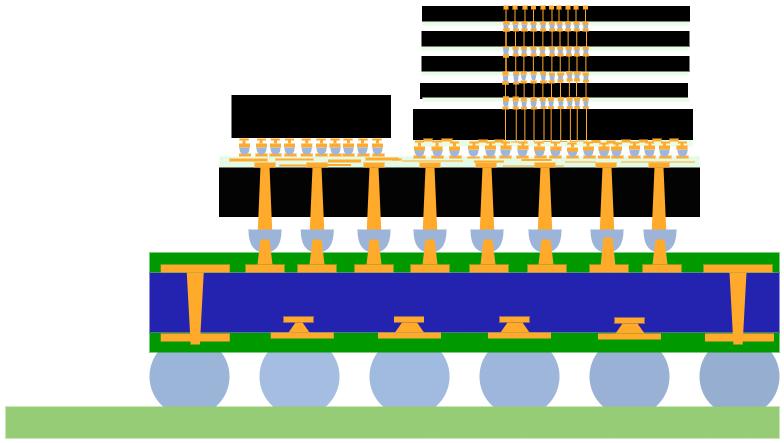

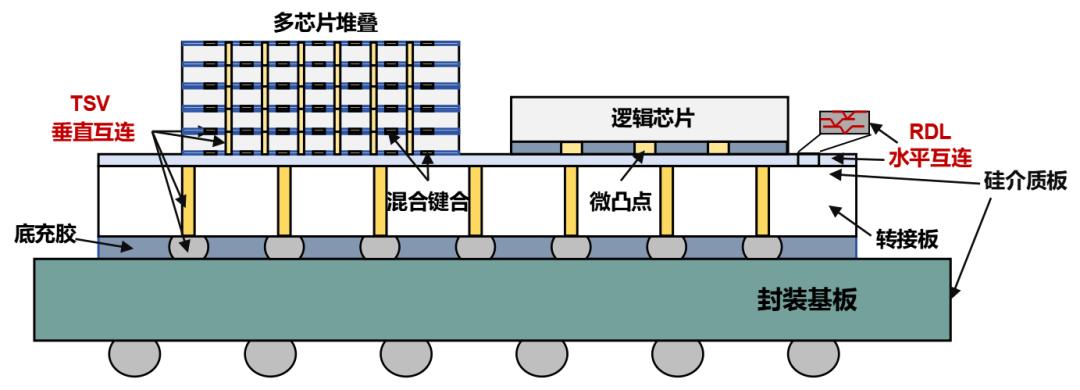

最广泛使用的2.5D封装方法,是通过硅中介层( Interposer)将内存和逻辑芯片(GPU或CPU等)放入单个封装。

2.5D封装需要用到硅通孔(TSV )、重布线层(RDL )、微型凸块等核心技术。

3D封装是在同一个封装体内,于垂直方向叠放两个以上芯片的封装技术。

2.5D和3D封装的主要区别在于:

2.5D封装,是在Interposer上进行布线和打孔。而3D封装,是直接在芯片上打孔和布线,连接上下层芯片堆叠。相对来说,3D封装的要求更高,难度更大。

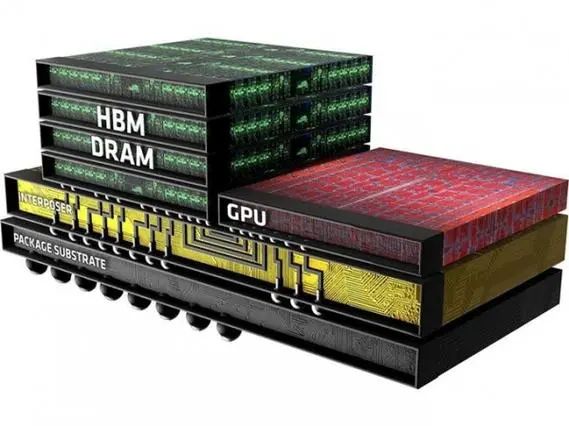

2.5D和3D封装起源于FLASH存储器(NOR/NAND )及SDRAM的需求。大名鼎鼎的HBM(High Bandwidth Memory, 高带宽存储器),就是 2.5D和3D封装的典型应用。将HBM和GPU进行整合,能够进一步发挥GPU的性能。

HBM,对于GPU很重要,对AI也很重要

HBM通过硅通孔等先进封装工艺,垂直堆叠多个DRAM,并在Interposer上与GPU封装在一起。HBM内部的DRAM堆叠,属于3D封装。而HBM与GPU合封于Interposer上,属于2.5D封装。

现在业界很多厂商推出的新技术,例如 CoWoS、HBM、Co-EMIB、HMC、Wide-IO、Foveros、SoIC、X-Cube等,都是由 2.5D和3D封装演变而来的。

系统级封装(SiP)

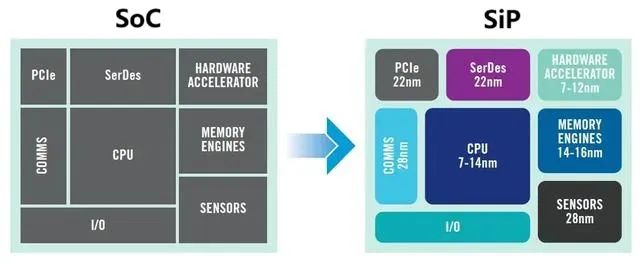

大家应该都听说过SoC (System on Chip, 系统级芯片)。我们手机里面那个主芯片,就是SoC芯片。

SoC,简单来说,是将多个原本具有不同功能的芯片整合设计到一颗单一的芯片中。这样可以最大程度地缩小体积,实现高度集成。

但是,SoC的设计难度很大, 同时还需要获得其他厂商的IP(intellectual property)授权,增加了成本。

SiP(System In Packet,系统级封装),和SoC就不一样。

SiP将多个芯片直接拿来用,以 并排或叠加的方式(2.5D/3D封装),封装在一个单一的封装体内。

尽管SiP没有SoC那样高的集成度,但也够用,也能减少尺寸,最主要是更灵活、更低成本( 避免了繁琐的IP授权步骤)。

业界常说的Chiplet(小 芯粒、小芯片),其实就是SiP的思路, 将一类满足特定功能的裸片( die),通过die-to-die的内部互联技术,互联形成大芯片。

硅通孔(TSV)

前面反复提到了硅通孔( through silicon via,TSV,也叫硅穿孔 )。

所谓硅通孔,其实原理也挺简单,就是在硅介质层上 刻蚀垂直通孔,并填充金属,实现上下层的垂直连接,也就实现了电气连接。

由于垂直互连线的距离最短、强度较高,所以,硅通孔可以更容易实现小型化、高密度、高性能等优点,非常适合叠加封装(3D封装)。

硅通孔的具体工艺,我们下期再做介绍。

重布线层(RDL)

RDL是在芯片表面沉积金属层和相应的介电层,形成金属导线,并将IO端口重新设计到新的、更宽敞的区域,形成表面阵列布局,实现芯片与基板之间的连接。

RDL技术

说白了,就是在硅介质层里面重新连线,确保上下两层的电气连通。在3D封装中,如果上下堆叠的是不同类型的芯片(接口不对齐),则需要通过 RDL重布线层,将上下层芯片的IO进行对准。

如果说TSV实现了Z平面的延伸,那么,重布线层(RDL)技术则实现了X-Y平面进行延伸。业界的很多技术,例如WLCSP、FOWLP、INFO、FOPLP、EMIB等,都是基于RDL技术。

扇入(Fan-In)/扇出(Fan-Out)型晶圆级封装

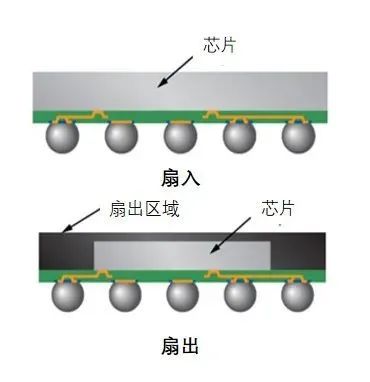

WLP(晶圆级封装)可分为扇入型晶圆级封装(Fan-In WLP)和扇出型晶圆级封装(Fan-Out WLP)两大类。

扇入型直接在晶圆上进行封装,封装完成后进行切割,布线均在芯片尺寸内完成,封装大小和芯片尺寸相同。

扇出型则基于晶圆重构技术,将切割后的各芯片重新布置到人工载板上。然后,进行晶圆级封装,最后再切割。布线可在芯片内和芯片外,得到的封装面积一般大于芯片面积,但可提供的IO数量增加。

目前量产最多的,是扇出型产品。

以上,小枣君尽可能简单地介绍了一些封装的背景知识。

下一期,我要开始介绍封装的主要工艺。敬请关注!

参考文献:

1、《芯片制造全工艺流程》,半导体封装工程师之家;

2、《 一文读懂芯片生产流程》,Eleanor羊毛衫;

3.、《 不得不看的芯片制造全工艺流程》,射频学堂;

4、《 什么是先进封装?和传统封装有什么区别?如何分类?》, 失效分析工程师赵工;

5、《 一文了解先进封装之倒装芯片(FlipChip)技术》, 圆圆的圆,半导体全解;

6、《 一文了解硅通孔(TSV)及玻璃通孔(TGV)技术》,圆圆的圆,半导体全解;

7、《 先进封装发展充要条件已具,关键材料国产替代在即》,国金证券;

8、《 Chiplet先进封装大放异彩》,民生证券;

9、维基百科、百度百科、各厂商官网。