(图片来源: 英特尔)

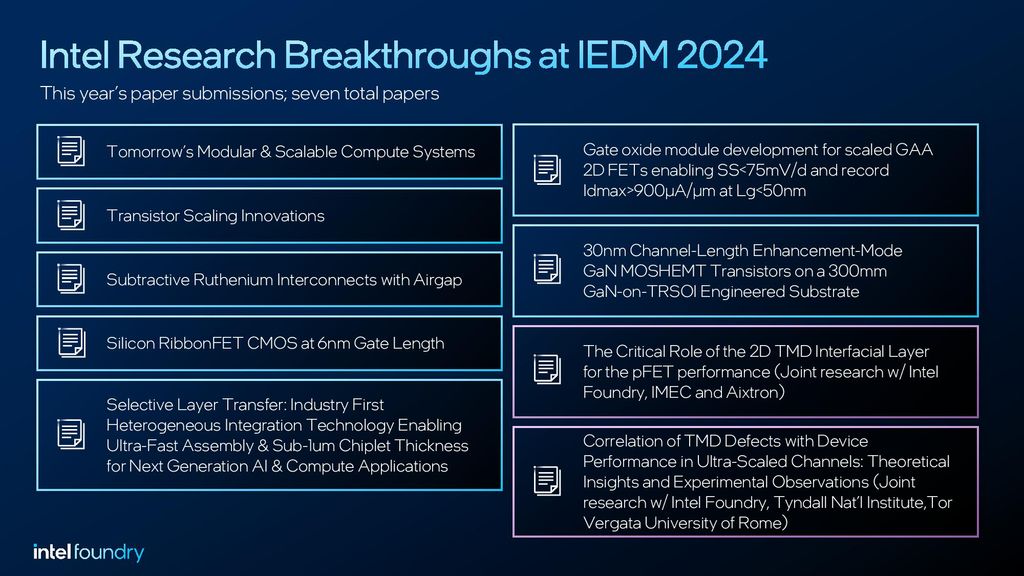

今日,英特尔代工技术研究团队宣布了在2D晶体管技术、芯片互联和封装技术方面取得的重要突破,包括采用超越硅材料的GAA晶体管以及创新的芯片互联和封装技术。英特尔将在2024年IEEE国际电子器件会议(IEDM)上发表七篇研究论文,并与imec等行业伙伴共同发布另外两篇。

英特尔披露的内容涵盖了新材料研究,这些研究增强了环绕栅极(GAA)晶体管的缩放和性能,无论是基于硅材料还是原子级薄的2D晶体管(使用超越硅的材料)。此外,英特尔还介绍了其减法钌技术,该技术显著提升了互联性能和可伸缩性,实现了晶体管间更细的导线,并公布了一项芯片封装技术的突破,将芯片间组装吞吐量提高了100倍。

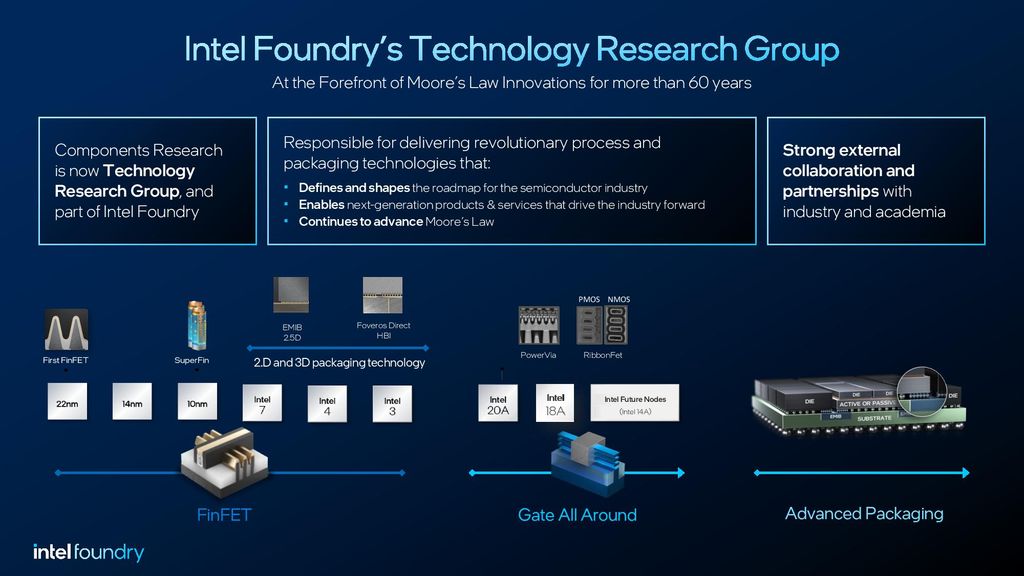

英特尔技术研究团队(过去50年被称为组件研究团队)是英特尔代工的重要组成部分,专注于开发预期在短期内可实现商业化的产品,与英特尔实验室的长远规划相比,更侧重于短期目标的实现。该团队以引领英特尔多项基础技术的发展而闻名,包括最新的PowerVia背面电源传输和RibbonFET环绕栅极架构等创新。

尽管英特尔尚未在IEDM上发表论文,我们与研究团队总经理的一对一讨论也将等到明天进行。以下是对这些突破的初步介绍,后续将补充更多细节。

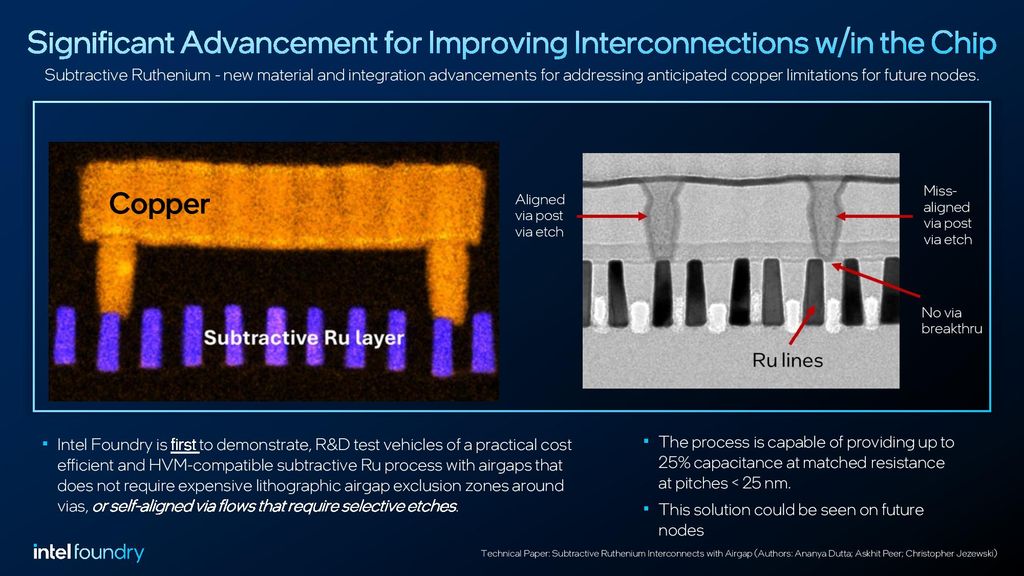

互联技术的新突破

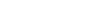

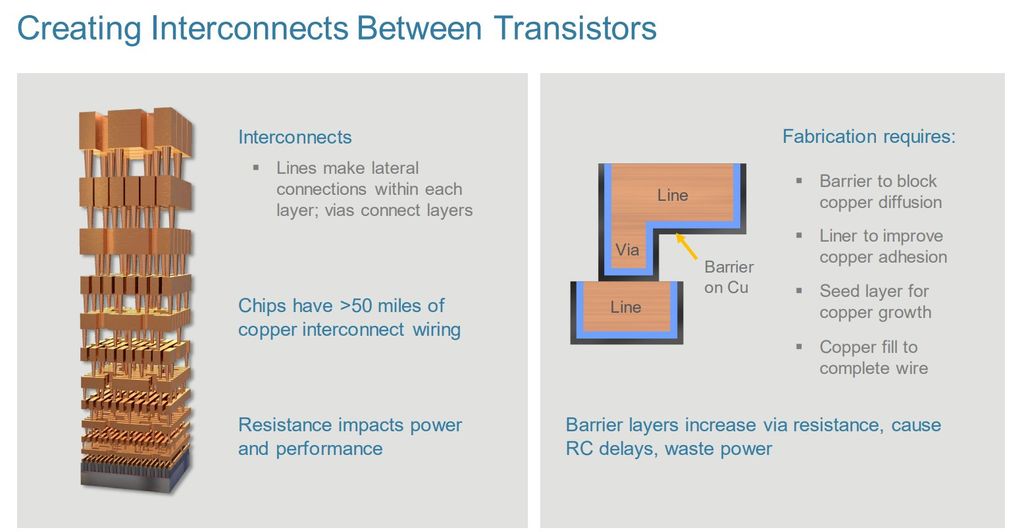

随着晶体管的不断缩小,连接它们的导线(互联)也必须相应缩小。铜是数十亿条纳米级导线的首选材料,这些导线在复杂的3D网格内传输电力和数据(您可以在此视频中看到其结构)。事实上,现代芯片内部包含多达50英里的互联导线。然而,微观导线缩小的能力已接近极限,且大多数替代材料均不适合大规模生产,这成为向更小工艺节点迈进的关键障碍。

(图片来源: Destination 2D)

与家中电气设备使用的标准铜线类似,晶体管间传输电子的导线也需要绝缘层以防止电子逸散,但这给导线缩小带来了挑战。

由于铜大马士革工艺的要求,处理器中互联导线的缩小极为困难。这是一种添加工艺,首先创建沟槽,然后沉积作为绝缘体的阻挡层,再放置籽晶层进行铜电镀,最后沉积铜并抛光多余材料。然而,减少铜量虽有助于导线变薄,却会降低铜与阻挡层和籽晶层的比例,导致电阻率随导线缩小而指数级增加,进而影响电流承载能力和设备速度。

(图片来源: 英特尔)

英特尔技术研究团队开发了一种适合大规模生产的工艺,采用钌替代铜,并使用气隙替代阻挡层(英特尔早在14nm工艺节点就已引入此技术)。这种创新使用空气作为绝缘体(介电常数约为1.0),不仅显著提高了电容(英特尔声称在14nm时电容提高了17%),还通过减法钌工艺实现了更细的导线。

尽管英特尔未透露减法钌工艺的详细细节,但通常该工艺涉及沉积钌、使用光刻胶图案定义互联形状,并通过蚀刻去除多余材料以形成图案化互联。我们期待在演示中了解更多详情。

英特尔表示,其带有气隙的减法钌工艺在低于25nm间距时,能在匹配电阻下提供高达25%的电容提升。研究团队“首次在研发测试车辆中展示了实用、经济高效且适合大规模生产的带有气隙的减法钌集成工艺,该工艺无需围绕通孔的昂贵光刻气隙排除区,也无需自对准通孔流的选择性蚀刻。”

(图片来源: 应用材料公司)

英特尔计划首先在间距最小的关键层中应用该技术,而标准铜技术则用于不太敏感的上层。此外,该技术对PowerVia背面电源传输也大有裨益。最终,这些更细的导线将能连接更小的晶体管,英特尔表示这项技术有望在未来的代工节点中得到应用。

环绕栅极(GAA)晶体管的新突破

(图片来源: 英特尔)

(图片来源: 英特尔)

(图片来源: 英特尔)

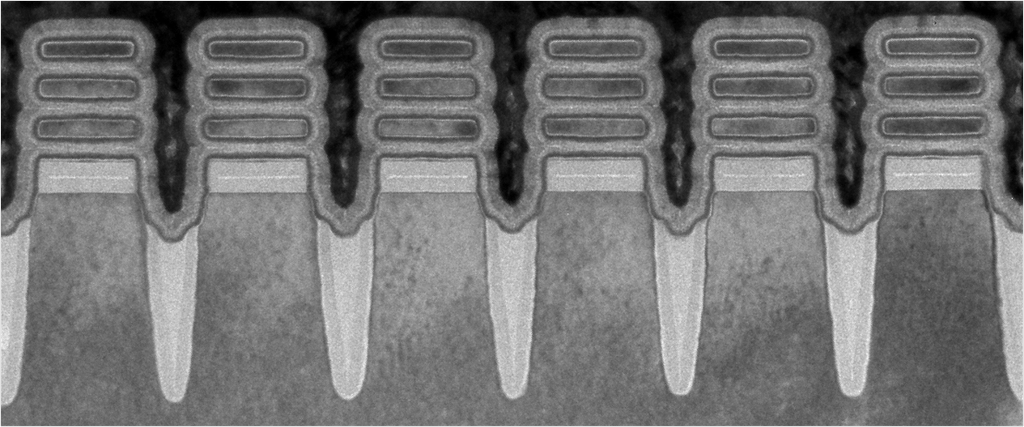

英特尔的RibbonFET是其自FinFET问世13年多来的首款新型晶体管设计,也是首款环绕栅极(GAA)晶体管,首次亮相于20A和18A节点。它采用完全被栅极包围的堆叠纳米片结构,而非FinFET中的三面包围鳍片。

(图片来源: 英特尔)

(图片来源: 英特尔)

(图片来源: 英特尔)

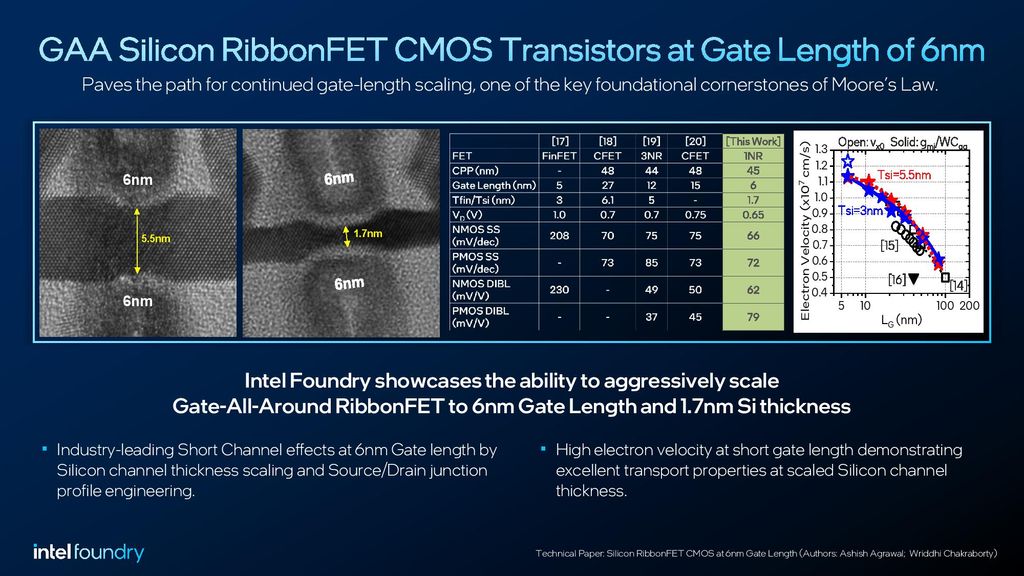

当前挑战在于如何进一步缩小GAA设计,英特尔正通过标准硅设计和新型2D材料两方面应对这一挑战。在标准硅方面,英特尔的晶体管技术可将栅极长度缩小至6nm,纳米带/纳米片厚度缩小至1.7nm,同时改善短沟道效应并提高性能。

右侧栅极长度与电子速度图展示了令人印象深刻的性能。与现有晶体管技术相比,纳米带的Tfin/Tsi(鳍片厚度/纳米带厚度)几乎是FinFET中鳍片的两倍。

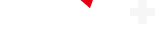

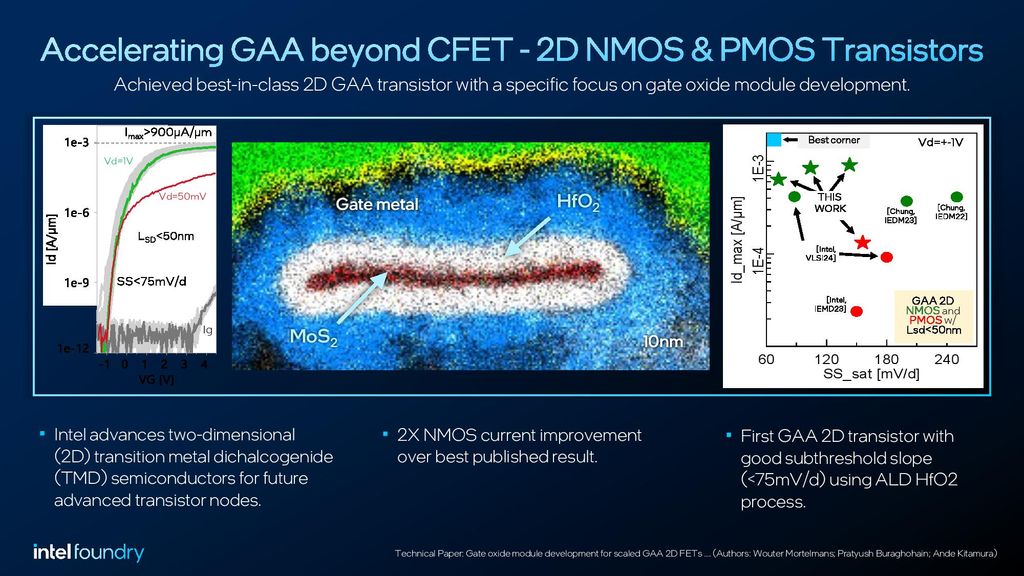

更大的问题在于硅之后的材料选择。在CFET晶体管之后,GAA的下一步是将NMOS和PMOS晶体管中的材料替换为仅有几原子厚的2D材料。第二张幻灯片概述了英特尔在使用原子级薄的过渡金属二硫化物(TMD)材料方面取得的进展,这些材料被广泛视为硅的潜在替代者。

英特尔利用基于钼的材料制造了栅极长度为30nm的2D环绕栅极NMOS和PMOS晶体管,声称提供了“同类最佳的NMOS驱动电流”,比次优结果高出2倍。右侧图表显示,该研究在探索TMD方面表现优异。

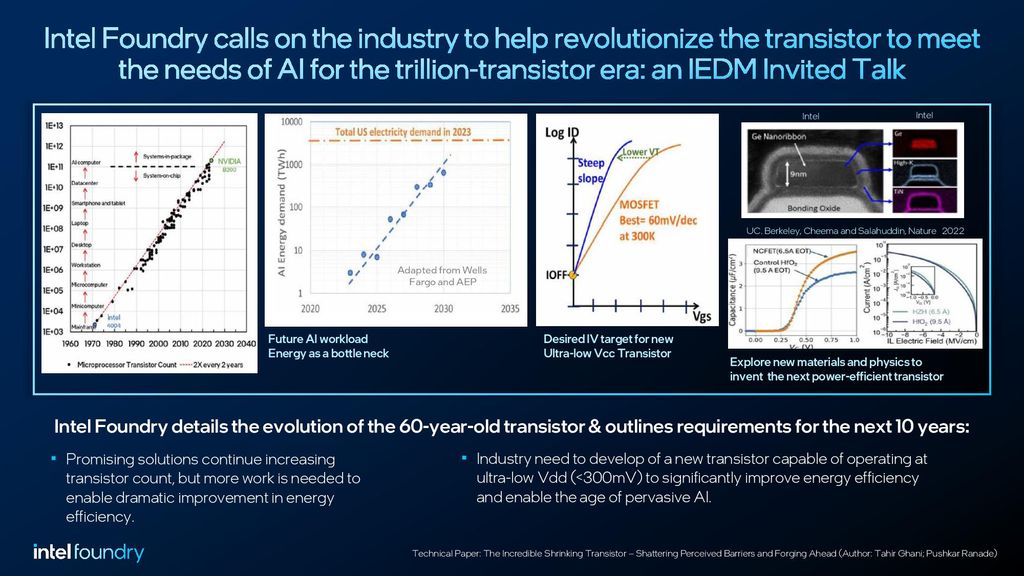

英特尔的晶体管发展轨迹还回顾了过去60年的晶体管技术,并呼吁业界开发能在超低Vdd(电源电压低于300mV,远低于当前的1V范围)下工作的晶体管。这是面向2030年代和2040年代的长期目标。

封装技术的新突破

(图片来源: 英特尔)

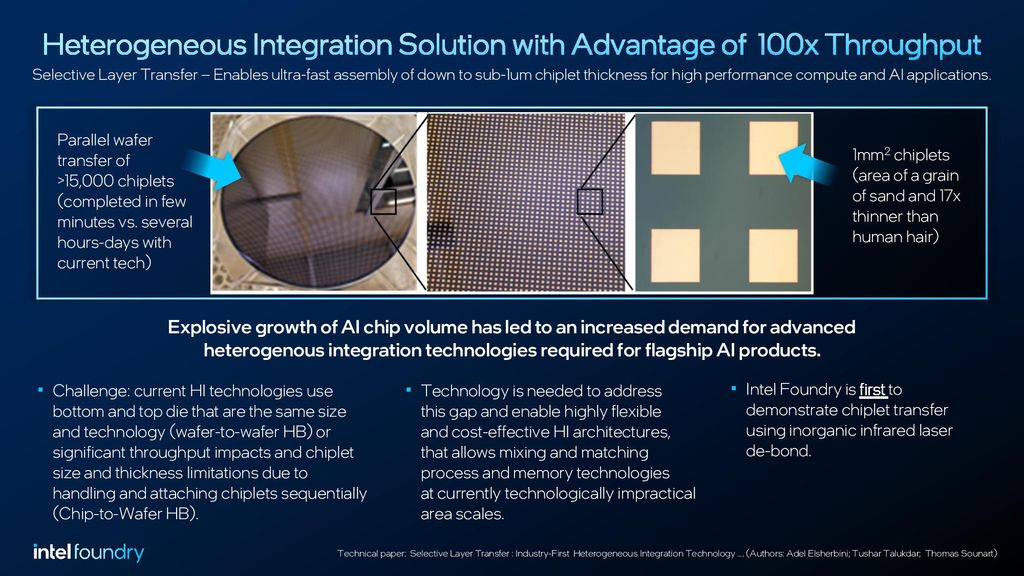

英特尔的新选择性层转移(SLT)技术能以极高速度将整个芯片晶圆附着到另一个晶圆上,据称可将芯片间组装过程的吞吐量提高100倍。SLT技术允许一次性将整个包含芯片的晶圆连接到下层晶圆,并可选择单个芯片进行键合,排除其他芯片。该技术采用无机红外激光解键合。

英特尔还指出,SLT“能实现超薄芯片,具有更好的灵活性,支持更小的芯片尺寸和更高的纵横比,相较于传统芯片到晶圆键合具有优势。”由于英特尔对这项新技术的描述尚不完全清晰,我们期待从演示中获取更多信息。这似乎是一种很好的替代方法,可替代使用重构晶圆的技术。一旦了解更多详情,我们将在此补充。

(图片来源: 英特尔)

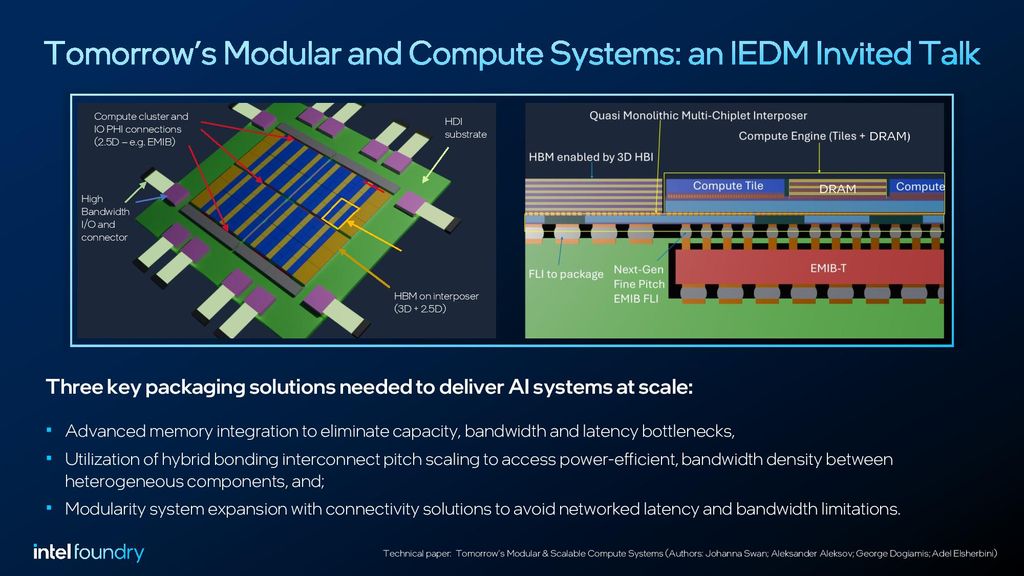

英特尔还将在明天的IEDM上发表演讲,介绍未来的封装解决方案。上述幻灯片揭示了之前未披露的EMIB-T技术。需要提醒的是,EMIB是英特尔的嵌入式多芯片互联桥接技术,是一种低延迟、低功耗和高带宽的互联技术,用于连接芯片。

英特尔透露,EMIB-T代表EMIB-TSV。这一变体标志着首个使用TSV通过桥接发送信号的EMIB实现,而非将信号环绕桥接。

(图片来源: CPUs)

(图片来源: CPUs)

(图片来源: CPUs)

(图片来源: CPUs)

在IEDM会议上,英特尔将提交七篇论文,并与imec、Aixtron公司及罗马Tor Vergata大学等合作伙伴联合发表另外两篇论文。

我们已与英特尔约定了后续问题的讨论时间,并将尽快更新本文,以提供更多详细信息。