在此前的ISSCC上,英特尔SVP Navid Shahriari发布了题为《AI Era Innovation Matrix 》的演讲。他指出,人工智能具有改变人类的潜力,它提高了我们快速准确地解决复杂问题的能力,并开启了创新和理解的新领域。人工智能的发展速度之快是史无前例的,这要求系统层面的快速发展,从低功耗和边缘人工智能设备到基于云计算的计算,以及连接它们的通信网络。这种对快速人工智能系统扩展的需求正在推动硅片、封装、架构和软件领域的创新前沿。

在演讲中,Navid Shahriari介绍了一系列技术。在他看来,这些技术使行业能够在从芯片到系统的各个层面取得显著进步。他重申,人工智能 (AI) 的快速发展将传统计算技术推向极限,需要可持续且节能的解决方案来实现并行计算系统的指数级扩展。计算行业必须满足所有行业对计算能力、内存带宽、连接性、高性能基础设施和 AI 日益增长的需求。

在本文中,作者着重强调了图 1.1.1 所示的技术矩阵的进步,从软件和系统架构到硅片和封装。每个领域的进步都是必要的,但整个系统必须共同优化,以最大限度地提高性能、功耗和成本。强大的生态系统伙伴关系和新颖的设计方法对于高效的共同优化和更快的上市时间至关重要,为 AI 的变革潜力奠定了基础。

芯片

芯片微缩一直是半导体行业进步的基本驱动力,并且仍然是创新矩阵的基石。硅片路线图由非增量晶体管和互连架构进步、High NA EUV 光刻以及相关的掩模和建模解决方案实现。每代技术的功能扩展和改进都由设计技术协同优化 (DTCO) 流程指导,该流程设定并推动逻辑、内存和模拟/混合信号功率、性能、面积 (PPA) 和成本扩展的整体目标。设计和工艺技术之间的这种迭代循环对于实现持续的硅片微缩优势至关重要。

一、RibbonFET

RibbonFET 是一种全栅极晶体管,超越了 FinFET 架构,提供性能扩展和工作负载灵活性 [1]。不同的带状宽度可在同一技术基础上为不同的性能和效率需求提供定制解决方案。

二、PowerVia

PowerVia Power Via 是一种高产量背面供电技术,它集成了晶体管的供电,将 IR 压降降低了 5 倍,并为信号路由提供了额外的正面布线。它满足所有 JEDEC 热机械应力要求,零故障,并在硅片中显示出超过 5% 的频率优势。值得一提的是,英特尔 18A 是英特尔领先的工艺节点,将提供业界首个 RibbonFET 和 PowerVia 技术的组合。

三、Hign NA EUV 优势

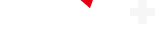

High NA EUV 可实现灵活的设计规则,减少寄生电容并提高性能 。它通过降低设计规则复杂性和多重曝光需求来简化电子设计自动化 (EDA) 的各个方面。Intel 14A 正面互连针对High NA 单次曝光图案进行了优化,提高了良率和可靠性(图 1.1.2)。

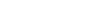

四、利用High NA EUV 为全场大型芯片 AI 应用赋能 AI

High NA EUV 工具的成像场(imaging field size)较小,但英特尔已开发出跨边界电缝合芯片的解决方案。EDA 生态系统正在创建支持这一点的工具,而掩模生态系统则致力于实现无需光罩缝合的全场尺寸能力(图 1.1.3),从而将生产率提高 23-50%。

五、利用 AI 和曲线掩模解决方案增强High NA EUV 优势

High NA EUV 光刻需要先进的建模和掩模解决方案。英特尔使用 AI 和机器学习来实现准确性,同时管理计算成本。曲线掩模提高了图案空间利用率、工艺窗口,并显着降低了可变性。

3D 集成电路 (3DIC)、封装和组装

随着数据处理需求的增长,在更小的面积上实现更高的计算能力并降低能耗至关重要。3DIC 技术通过异构集成降低成本和占用空间,通过更高的带宽提高性能,并通过垂直堆叠降低功耗。先进节点上的基础芯片对于实现硅通孔 (TSV) 和先进接口、无缝集成 3D 元素至关重要。

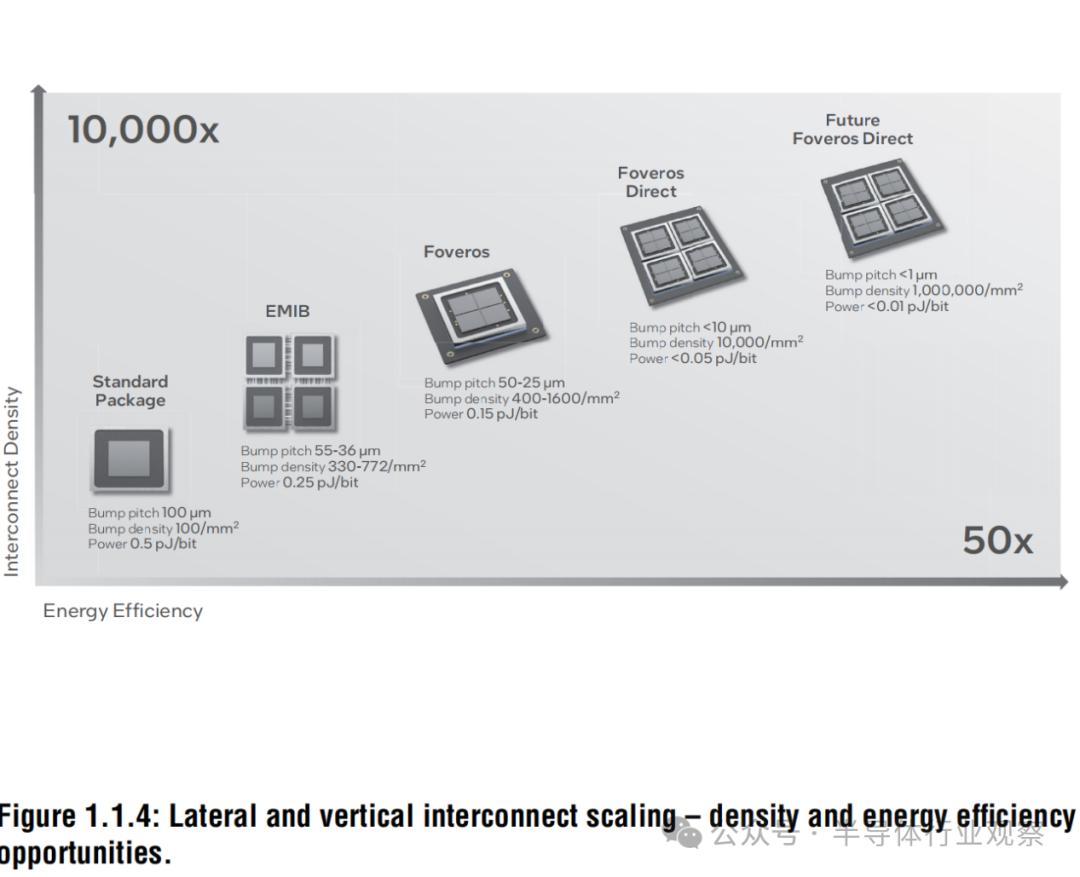

封装上的垂直和横向互连必须继续扩展,以提供更高的互连密度,从而实现带宽增长和提高能源效率(图 1.1.4)。经济高效的互连扩展,结合使用基于标准化的链路(如 UCIe),对于创建芯片生态系统至关重要,在该生态系统中,即插即用将实现产品多样性和定制化。

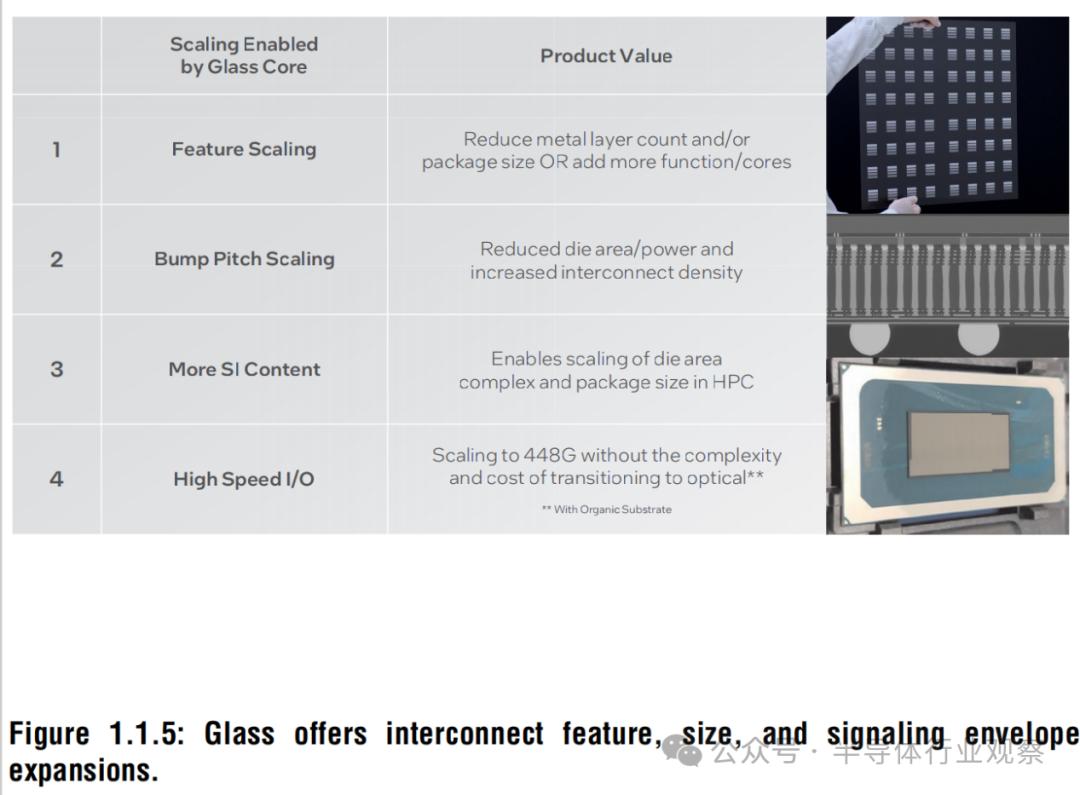

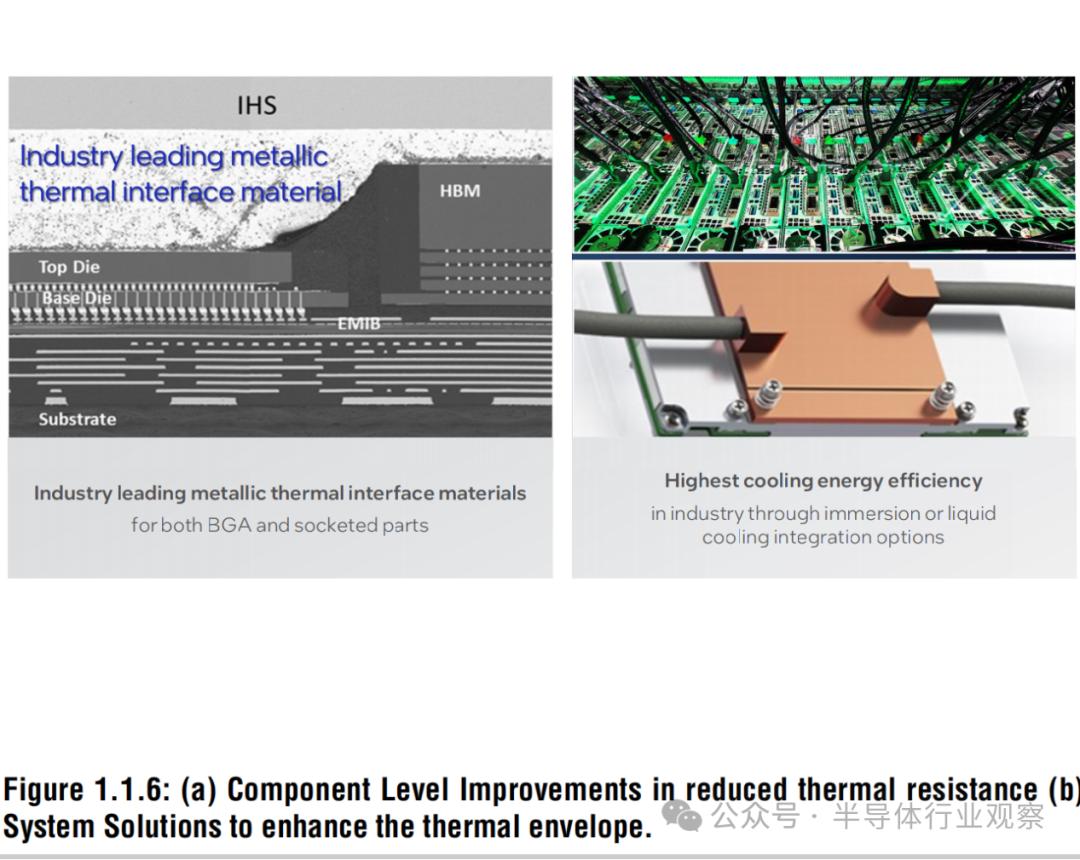

成熟地使用玻璃来缩放封装基板互连几何形状、尺寸和信号特性(图 1.1.5)是一项重要的技术载体。必须通过提高系统级功率传输效率(稍后介绍)并通过组件和系统级创新扩大热范围(图 1.1.6)来解决 AI 应用对功率不断增长的需求。

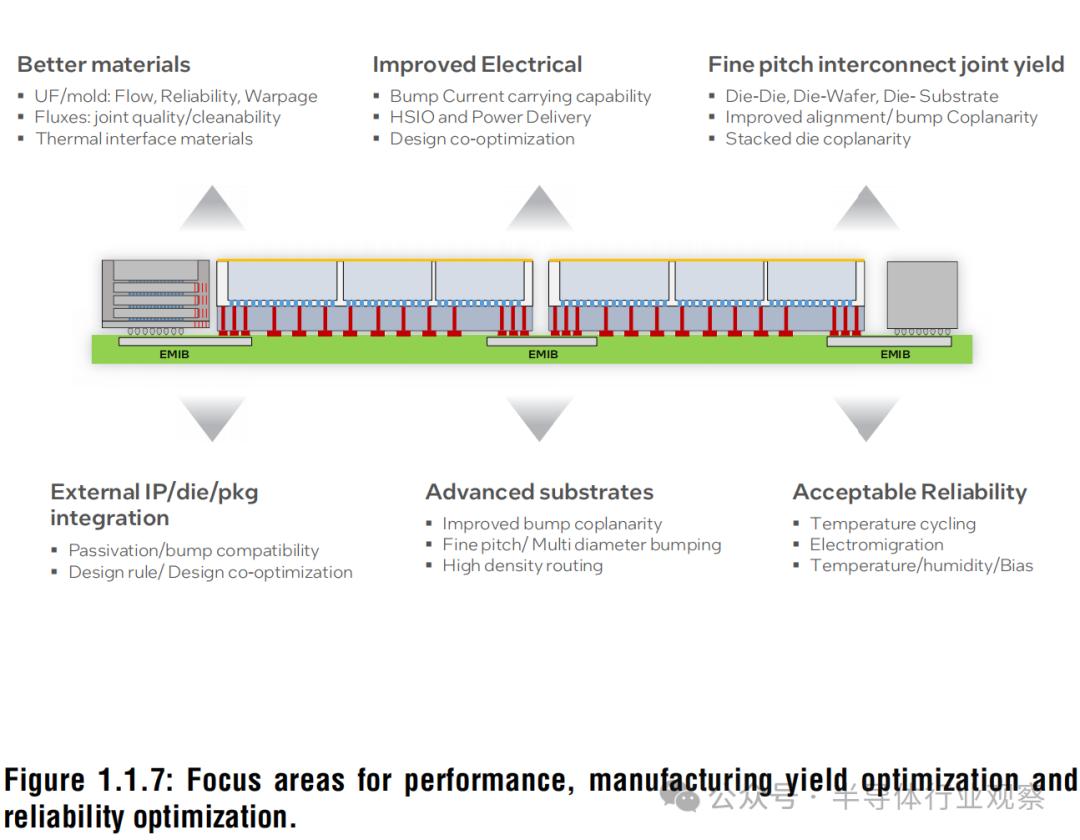

先进封装技术的发展方式是,随着特征尺寸和制造工艺的重叠,封装和硅后端互连之间的界限越来越模糊。此外,封装变成了一个复杂的异构结构。制造和测试工艺必须不断发展,以确保良率保持较高水平(图 1.1.7)。模块化设计环境允许直接组装多硅、共封装系统,从而优化成本、性能和带宽,这一点至关重要。需要全面的 EDA 工具和流程功能来实现跨芯片的设计分区,从而实现成功的共同设计以及芯片和封装的优化。

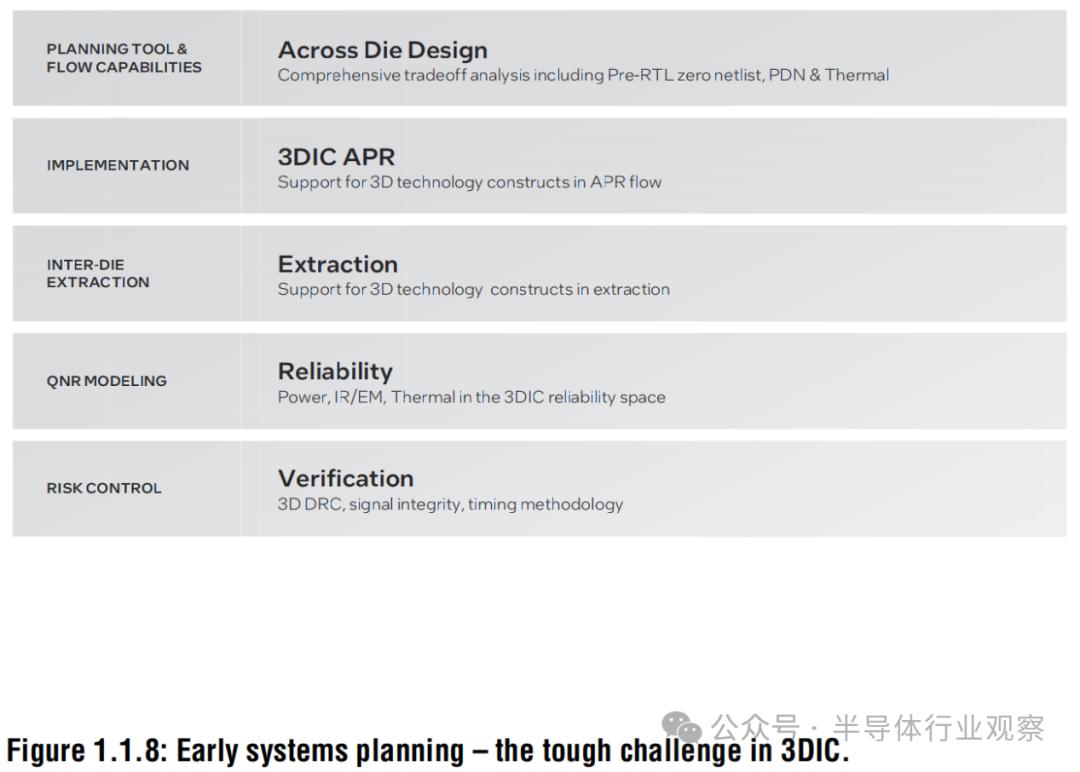

当前的 3DIC 设计流程缺乏热应力和机械应力建模,导致潜在的故障和重新设计工作,从而影响上市时间。3DIC 设计工具必须涵盖实施、提取、可靠性和验证,以确保无缝集成(图 1.1.8)。

互连

并行 AI 工作负载的指数级扩展给互连带宽密度、延迟和功率带来了压力。如上所述,通过使用密集的 2.5D 和 3D 组装技术更紧密地集成组件,可以改善这三个指标。新的封装技术通过最小化 GPU 之间非常昂贵的(价格和功率)互连来提供更好的总拥有成本 (TCO)。传输每位数据的能量与通道损耗成比例 。这种权衡推动了行业规范的定义,例如 UCIe,用于低功耗、高密度封装通信。UCIe 在 <1pJ/bit 时每毫米芯片周长可实现高达 1.35TB/s 的速度。

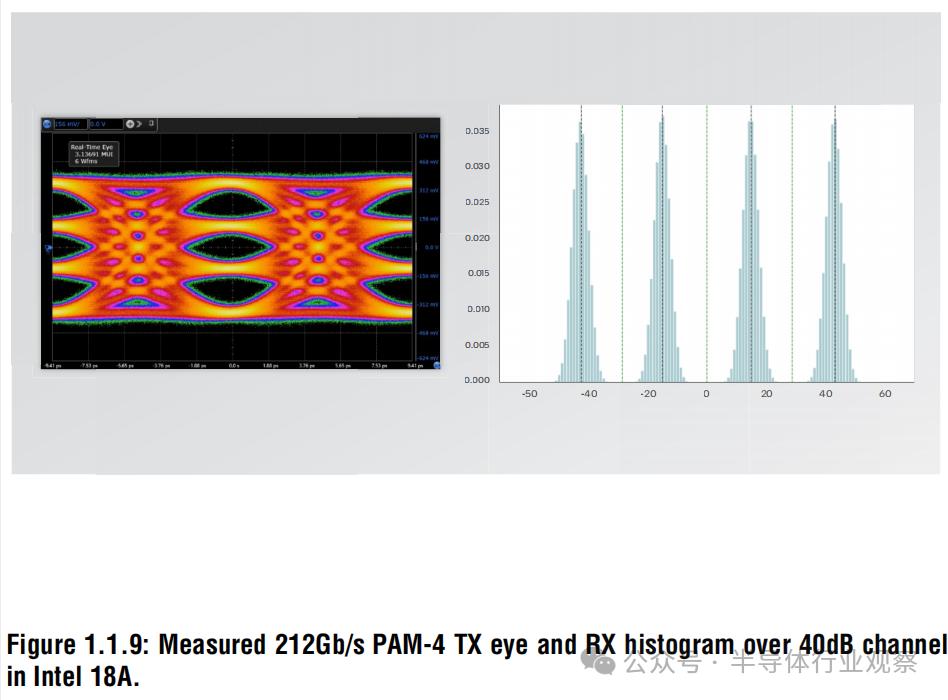

电路板和机架内的较长互连构成了扩展网络拓扑中的高带宽域,需要增加数据序列化以考虑实际连接器信号密度,从而扩大总带宽。每通道串行数据速率每 3-4 年按 2 倍缩放,包括以太网、PCIe 和 OIF-CEI 等行业规范。最新生产的有线 SerDes 已达到 212Gb/s PAM4,以 4-6pJ/bit 的速度支持机架内(约 1 米范围)通信。模拟电路的每比特能量和数字均衡都继续受益于工艺技术的扩展。

图 1.1.9 显示了在 40dB 通道上以 Intel 18A 运行的 212Gb/s SerDes 的测量 TX 和 RX 眼图。随着有线互连数据速率不断提高,由于较高符号速率下的信道损耗更高,SerDes 重定时器之间可以桥接的距离会减少。

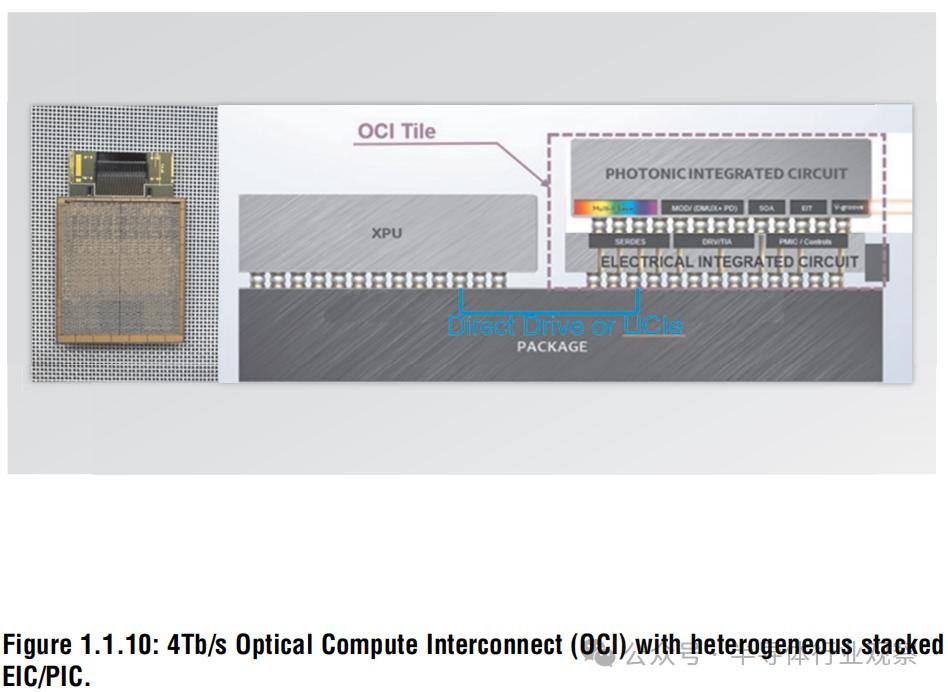

添加更多重定时器可以扩大覆盖范围,但会增加功率、延迟和成本。这种经验权衡导致在从海底电缆到机架到机架网络等一系列应用中采用光互连。此外,使用光学器件将高带宽域的覆盖范围扩展到机架之外符合 AI 的扩展网络策略。因此,光互连将需要移入机架以扩展带宽,

并达到可接受的功率范围。正在开发共封装光学器件 (CPO) 和直接驱动线性光学器件等技术来实现这一转变。

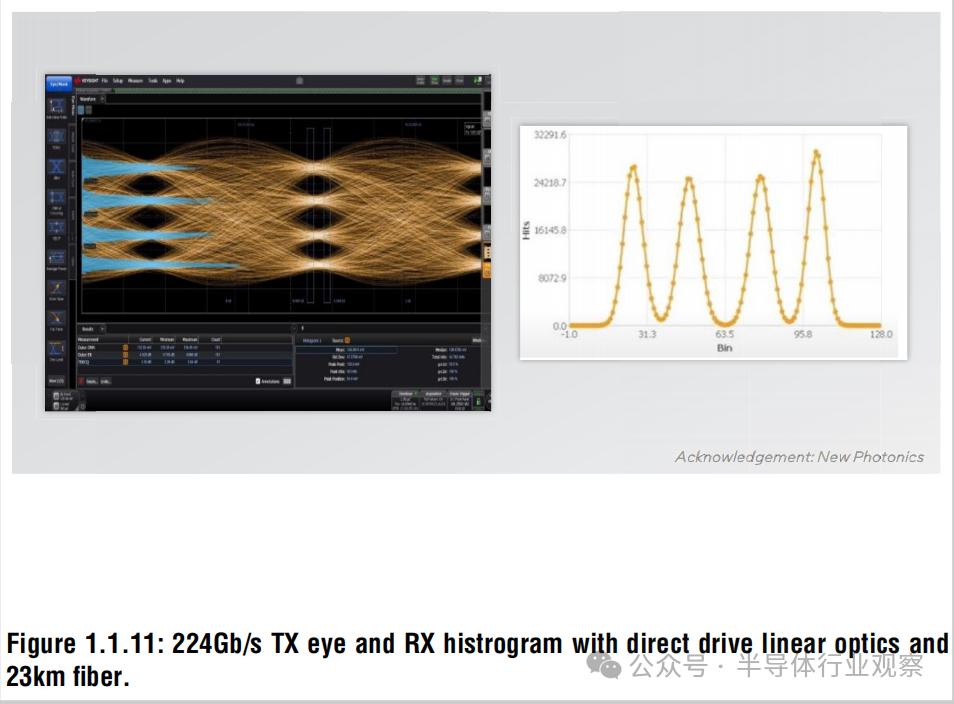

英特尔最近展示了一款基于英特尔内部硅光子技术的 4Tb/s(8 根光纤 × 8 波长/光纤 × 32Gbps/波长)双向全集成光计算互连 (OCI) 芯片(图 1.1.10)和 23 公里光纤上的 224Gb/s PAM4,采用直接驱动线性光学器件(图 1.1.11)。整个行业正在努力加速这一机架内光互连生态系统,开发高良率的制造工艺、材料和设备,同时提高带宽密度、总功率、可靠性和成本。

电源输送

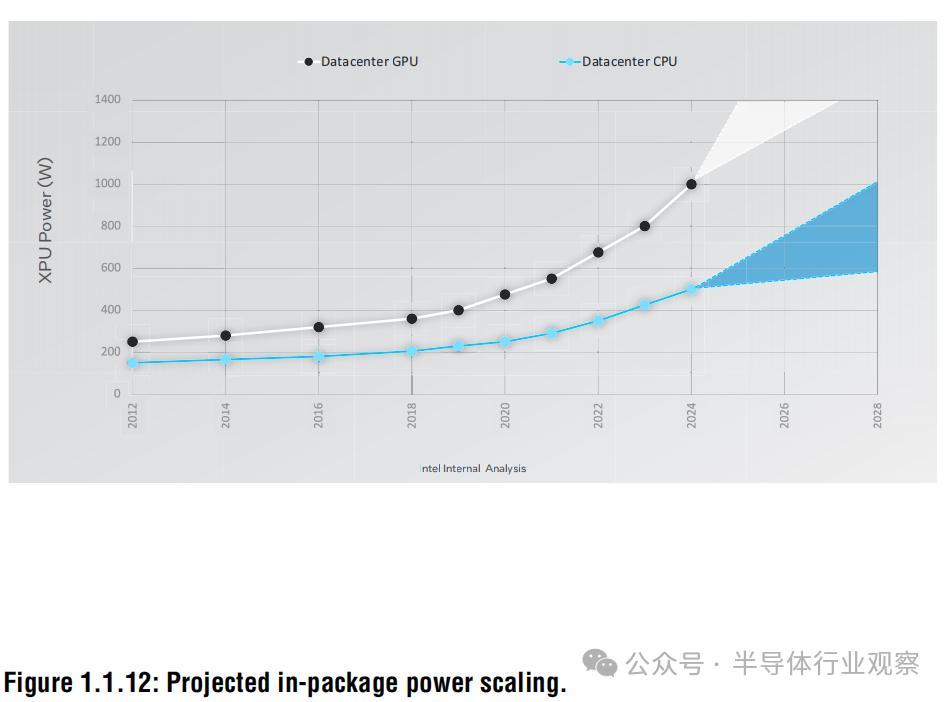

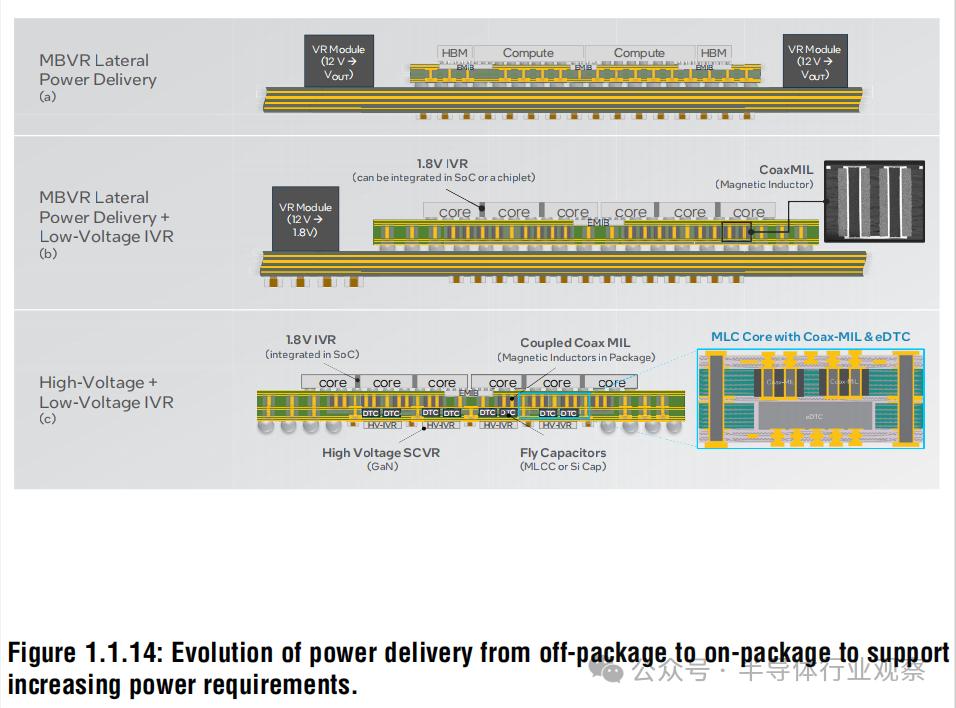

用于 AI 等并行工作负载的每封装功率正在迅速扩大(图 1.1.12)。为封装供电的常见方法是主板电压调节器 (MBVR:mother board voltage regulators)(图 1.1.14(a))。这些调节器将板级电源(例如 12V)降低到封装上芯片使用的电压(VOUT)。无论是放置在封装旁边(横向 MBVR)还是封装下方(垂直 MBVR),MBVR 提供的电流密度都无法跟上未来高性能芯片的步伐。

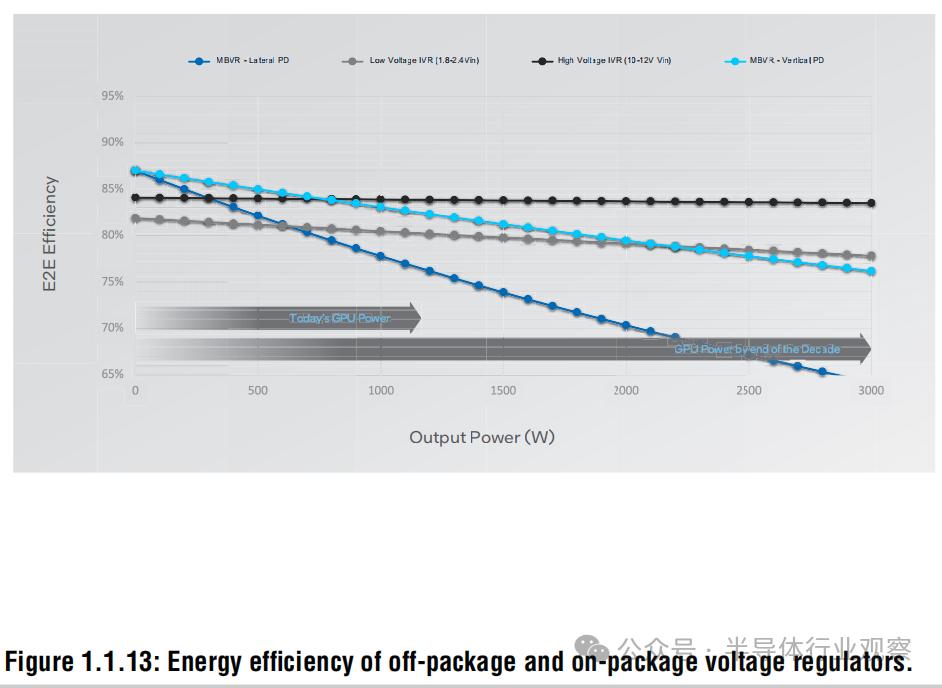

此外,随着功率和电流的增加(I2R 损耗),调节器效率会降低,从而降低系统性能(图 1.1.13)。

为此,我们需要解决方案将电压转换更靠近芯片,并具有高电流密度、转换效率和调节带宽。一个解决方案是使用完全集成的电压调节器 (FIVR:fully integrated voltage regulators ),将电源转换的最后一步带到封装上(图 1.1.14(b))。在封装上进行最终电压降压可通过降低给定功率的电流来减少将电源轨布线到封装上时的能量损失(图 1.1.13)。

英特尔十多年前首次在 Haswell 产品中引入 FIVR ,使用密集的片上电容器和空芯封装电感器。第一代 FIVR 将 1.8V 输入电源轨转换为多个片上电压域。在过去十年中,这种架构已在许多产品中使用,并进行了渐进式改进,例如更密集的封装磁电感器和片上电容器。

除了集成到 SoC 中的 FIVR 之外,英特尔还开发了基于 CMOS 的独立 2.4V IVR 芯片,该芯片使用英特尔的高密度电容器 (HDMIM) 技术开发了具有连续可扩展电压转换比的开关电容稳压器 (SCVR:switched-cap voltage regulator) 。如果使用现有的 MBVR 架构,封装内功率容量进一步扩展至 1-2kW 以上,则稳压器效率将出现不可接受的下降,如图 1.1.12 所示。通过将高压 (12V) 功率转换集成到封装上,可以缓解此问题。12V 稳压器集成将减少传输到封装中的电流,从而减少I2R 损耗。

一种有前途的方法是将封装上的高压 (12V) 开关电容稳压器 (SCVR) 与低压 (1.8-2.4V) IVR 配对,实现两步转换(图 1.1.14(c))。这种两步架构的功率密度和效率依赖于密集的封装无源器件,如嵌入式深沟槽电容器 (eDTC) 和磁电感器,以及密集的片上电容器。

使用氮化镓 (GaN) 等宽带隙工艺技术可以使高压转换器具有比基于硅的解决方案更高的效率和密度。然而,功率转换器的封装实现需要更高的开关频率和集成驱动器,而这在仅使用 GaN 的工艺上是无法支持的。

使用硅 CMOS 制造 GaN 器件可以为高压功率转换器的封装集成提供更多机会,因为它可以在同一芯片上设计 CMOS 驱动器和 GaN 功率 FET。为此,英特尔最近展示了一项在同一 300 毫米晶圆上结合硅基 GaN 技术的技术 。该技术可支持输入电压高达 12V 的高压 IVR 选项,从而实现 1-2 kW 以上的功率扩展。

架构和软件

下一代计算架构必须推动系统性能指标(如每瓦性能-美元-毫米²)的指数级改进,同时解决热和功率完整性挑战。创新应通过先进的封装和硅工艺堆叠和互连晶圆和小芯片来实现有凝聚力的系统。此外,它们还必须支持无缝集成各种工作负载的定制加速器 。

软件是创新矩阵的重要组成部分,必须通过开源生态系统中的协作、标准化和互操作性来发展。自动化应增强安全性并简化流程,而高度优化的软件对于高效利用硅资源至关重要。在数千个 GPU 上分发软件会带来巨大的带宽和延迟挑战,例如高性能计算。人工智能软件将成为微调系统元素、确保无缝集成和实现显著进步的关键。

超越传统计算

神经形态和量子计算等技术对于实现 AI 扩展所需的效率和速度突破至关重要。自 2018 年以来,全球超过 250 个实验室都在使用英特尔的 Loihi 研究芯片,该芯片表明,采用 CMOS 工艺技术制造的神经形态芯片可以为广泛的示例算法和应用带来数量级的增益 。虽然其中许多示例涉及目前与当今的软件和 AI 方法不兼容的新型大脑启发算法,但一类新兴技术表明,在不久的将来,当今广泛使用的深度学习和转换器方法将实现 1000 倍的增益 。

这些神经形态创新对于将先进的 AI 功能扩展到在实时设置下运行的功率、延迟和数据受限的智能设备至关重要。量子计算代表了一种新范式,它利用量子物理的力量以比传统计算快得多的速度解决复杂问题。它有望彻底改变行业并解决关键问题,包括气候变化、化学工程、药物设计和发现、金融和航空航天设计。稳步推进将这项变革性技术从实验室转移到工程领域,为有用的近期应用提供客户解决方案至关重要。英特尔独特的量子研究方法涵盖了整个计算堆栈,包括量子比特制造 、用于量子比特控制的低温 CMOS 技术、软件、编译器、算法和应用程序。

凭借 50 多年的大规模晶体管制造经验,英特尔正在利用其成熟的技术开发硅自旋量子比特,作为量子计算可扩展性的最佳前进方向。英特尔还在投资定制设计的低温探测器等功能,这些功能可大大加快英特尔量子测试和验证工作流程。量子计算硬件的现状还不具备对当今人工智能产生直接影响的稳健性和规模。人工智能使用量子计算机面临的另一个挑战是如何将大量数据输入这些复杂的机器。

然而,一旦我们拥有了可扩展的容错量子计算机,就会带来明显的好处。量子计算机可以比传统计算机更快地执行复杂计算,这可以加快人工智能模型的训练和分析速度。量子计算的两个关键原理是叠加和纠缠,它们可以同时探索多种解决方案,这可以直接有利于人工智能模型的训练和优化。并行分析大量数据的可能性也可以提高人工智能识别模式的能力,例如在图像或语音中。可以开发直接优化以利用量子特性的新人工智能算法,而不是使用传统人工智能算法。

最后,量子计算机不应被视为传统计算机的替代品,而应被视为特殊应用的计算加速器。因此,未来人工智能的系统解决方案可能会利用经典计算和量子计算的混合实现。

生态系统协作

快速开发下一代先进计算系统需要整个行业生态系统就此创新矩阵展开协作。与整个技术堆栈中的最终用户和合作伙伴(从制造到设计工具,从 IP 到系统设计再到软件)进行合作,确保开发过程符合市场需求和时间表、环境可持续,并利用整个生态系统的关键学习和开发。系统级共同优化需要密切协作才能取得快速进展。跨学科专业知识和跨战略伙伴关系的知识共享对于高效解决问题和加速开发周期至关重要。利用跨行业优势并避免重复努力将使团队能够更有效地工作。

行业挑战与机遇

近二十年前,CPU 时钟频率扩展面临一个困境——持续追求指数级性能改进在功率密度方面遇到了瓶颈。

其结果是产生了一套新的并行处理器架构以及一系列用于硅、封装和散热、互连、电力输送和核心架构的支持技术。今天,我们处于类似的境地,指数级性能扩展(这次是为了支持 AI)遇到了功率、连接性和成本方面的根本挑战。

再次,我们的系统的增量扩展是不够的,我们需要新的方法来解决这个问题——一个 AI 创新矩阵。从工艺技术扩展到 3DIC 系统设计,再到电力输送、互连和核心架构,工程挑战层出不穷。我们需要综合这些领域的创新优势,以可制造、可持续且经济高效的方式满足行业对计算能力的需求。