1.英特尔资本近亿元投资韩国设备零部件厂商DS Techno;

2.传一加13将搭载“定制版”骁龙8 Gen 4,能效将超过苹果A18 Pro;

3.IEDM将展示CFET在5nm和7埃米方面取得的成果;

4.TCL华星首款印刷OLED产品试产 预计年底前正式量产;

5.台积电、英特尔将在IEDM上详细介绍2nm工艺;

6.分析人士:力积电、SBI合资晶圆厂终止建设属意料之中;

1.英特尔资本近亿元投资韩国设备零部件厂商DS Techno;

据业界消息人士透露,英特尔资本近日向韩国半导体设备零部件供应商DS Techno投资约180亿韩元(约9602.22万元人民币),成为DS Techno新的战略股东。此前在2022年,DS Techno还获得了三星电子的投资。

据了解,为了在2030年成为仅次于台积电的全球第二大晶圆代工厂,英特尔正寻求采购具有竞争力的材料和零部件。一位业内人士表示,“通过实现消耗性零部件供应链多元化,也将能够实现成本节约”。英特尔资本此举应该旨在强化英特尔晶圆代工领域的供应链。

资料显示,DS Techno成立于1990年,是一家开发和生产碳化硅(SiC)、硅(Si)、石英等半导体制造设备中使用的消耗性零部件的韩国公司。该公司向三星电子、SK海力士、美光、台积电、英特尔等全球主要半导体公司供应材料和零部件。

营收方面,DS Techno的销售额从2014年的278亿韩元增长到2023年的1032亿韩元,增长了三倍。同时,该公司也在扩大产能。DS Techno计划到2026年在原州市文幕(Wonju Munmak)工业园区投资702亿韩元建设一座新工厂,到2028年在阴城郡(Eumseong Daeso)工业园区投资1504亿韩元建设另一座新工厂。

有报道称,英特尔认识到了DS Techno的竞争力,认为该公司拥有可以直接供应的品质和生产管理能力。(校对/孙乐)

参考报道:https://www.investkorea.org/gwn-ch/bbs/i-1544/detail.do?ntt_sn=491306

2.传一加13将搭载“定制版”骁龙8 Gen 4,能效将超过苹果A18 Pro;

骁龙8 Gen 4的性能在一加13中得到了展示,当时该芯片获得了单核最高分之一,在多核成绩中甚至比苹果A18 Pro高出18%。在这些结果泄露时,并没有提到芯片的功耗,而后者是衡量智能手机芯片性能的一个关键指标。据一加的一位高管称,骁龙8 Gen 4据说是为即将推出的旗舰机定制的版本,在能效方面击败了苹果的高端芯片。

之前的测试结果显示,A18 Pro在Geekbench 6测试中略低于10000分时的功耗为12瓦;“定制版”骁龙8 Gen 4的功耗必须更低。

在微博上,一加高管蔡祖轩发表了一个大胆的声明,声称该公司将采用定制的骁龙8 Gen 4,在能效方面击败A18 Pro。作为对比,Jikanglucky透露,iPhone 16 Pro和iPhone 16 Pro Max所使用的苹果旗舰SoC在运行Geekbench 6时的最大功耗为12瓦,其单核和多核得分分别为3701分和9615分。

之前在Geekbench 6上曝光的一加13得分为3236和10049分,其中性能核心的频率为4.32GHz,效率核心频率为3.53GHz。高通很可能已经允许其手机合作伙伴定制骁龙8 Gen 4的频率,以获得性能优势,只要这些制造商能够控制发热即可。上述时钟频率相对较高,但并未提及芯片的发热情况或与功耗有关的任何信息。(校对/孙乐)

3.IEDM将展示CFET在5nm和7埃米方面取得的成果;

在今年12月即将于旧金山举行的国际电子元件会议(IEDM)上,英特尔试图重返芯片制造领域的前沿,而代工厂台积电(TSMC)则在定义这一前沿方面迈出了步伐。

台积电的研究人员将公布N2制造工艺,这是一种标称2nm的工艺,专为人工智能(AI)、移动和高性能计算(HPC)领域的计算而设计。另外,英特尔工程师将详细介绍RibbonFET(纳米片晶体管)的缩放情况。

在IEDM会议上,台积电的研究人员预计将报告称,与2022年推出的N3(标称3nm)工艺相比,N2的速度提高15%,功耗降低30%,芯片密度提高15%,甚至更好。

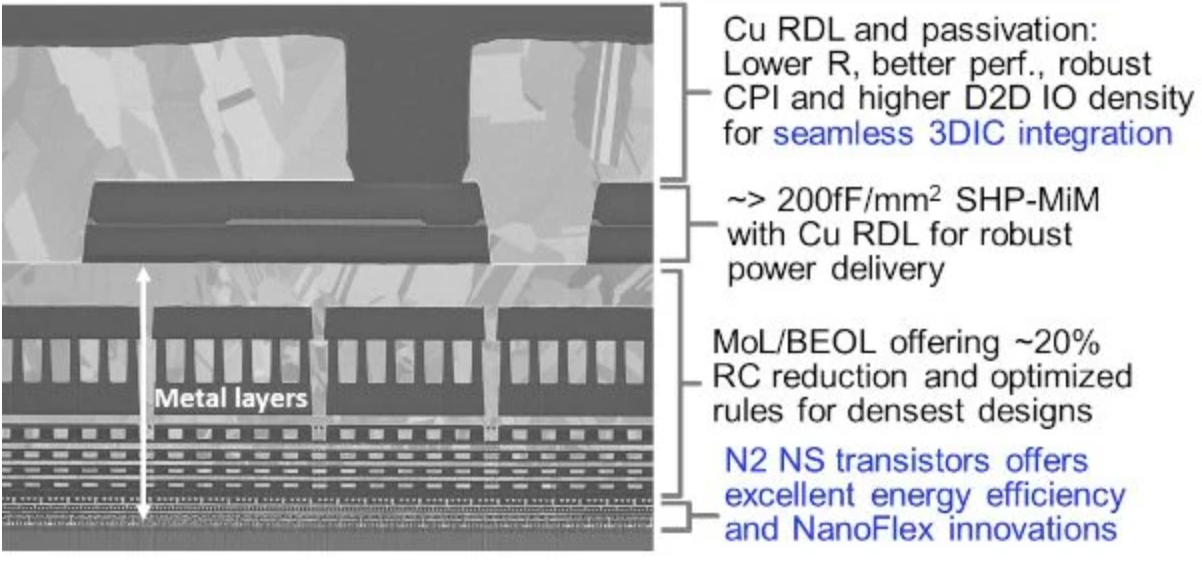

显示铜再分布层的N2互连堆栈截面图(来源IEDM)和T截面图显示,N2平台的铜再分布层 (RDL) 和钝化处理实现了与3D技术的无缝集成。

台积电的G. Yeap等人撰写的论文显示,2nm平台技术采用与3DIC协同优化的高能效纳米片晶体管和互连器件,适用于AI、HPC和移动SoC应用。也将展示具有世界纪录密度38Mbits /平方毫米的SRAM宏。

台积电论文还将详细介绍中段(MEOL)和后端(BEOL)互连,其特点包括:可扩展的铜基再分布层(用于灵活放置输入/输出焊盘,降低阻挡电阻);扁平钝化层(用于提高可靠性);硅通孔(TSV)(用于互连不同层中的设备)。

台积电研究人员表示,N2平台已达到晶圆级可靠性要求,并通过了初步鉴定测试。预计将于2025年通过全面鉴定,并于2026年实现量产。

英特尔的A. Agrawal等在论文中展示了他们如何在不降低电子迁移率的情况下,用6nm栅极和45nm接触多晶硅间距(CPP,晶体管栅极之间的间距)构建纳米片技术(RibbonFET)。

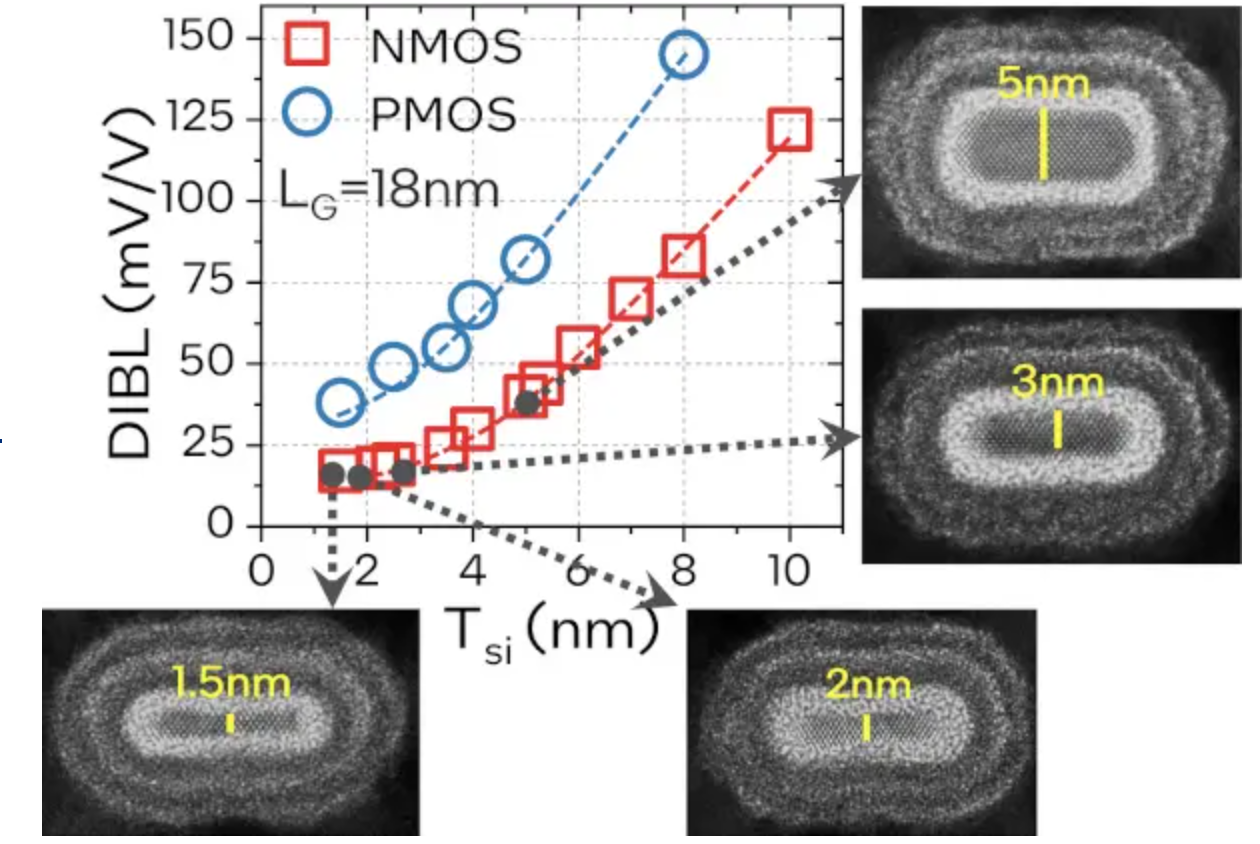

栅极长度为18nm时,漏极诱导势垒降低(DIBL)与硅厚度(Tsi)的关系显示,当Tsi从10nm缩放到1.5nm时,DIBL有所降低;然而,当Tsi <4nm时,DIBL降低达到饱和。与相同Tsi下的NMOS DIBL相比,PMOS DIBL有所提高。图中还显示了1NR晶体管的TEM显微照片,该晶体管的各种Tsi值均低至1.5nm。(来源:IEDM)。

研究人员没有提到英特尔的具体制造工艺,但RibbonFET计划采用Intel 20A工艺(标称20埃或2nm工艺)进行生产。英特尔似乎选择不在Intel 20A工艺上推出任何处理器产品,而是直接从3nm工艺转向Intel 18A(1.8nm)工艺,这可能反映在作者对纳米片缩放的关注上。

英特尔研究人员将证明,在纳米片硅厚度达到3nm之前,电子迁移率不会降低。此后,由于表面粗糙度造成的电子散射将成为一个问题。在论文中,作者报告了4nm以下硅厚度的短通道控制和功函数工程如何实现3nm的低阈值电压。(校对/张杰)

4.TCL华星首款印刷OLED产品试产 预计年底前正式量产;

据财联社报道,TCL科技子公司TCL华星印刷OLED中心中心长曹蔚然在接受采访时表示,目前公司正在为印刷OLED量产做准备,首款产品——医疗设备用显示屏已经在产线中试产,预计今年年底前正式量产。

据悉,印刷OLED技术相比于传统真空蒸镀工艺,印刷显示工艺简单,不需要昂贵的真空蒸镀机台和高精度金属掩膜板,材料利用率可达90%以上,不仅成本优势明显,而且可实现高 PPI和更长寿命。

消息称,TCL华星将在明年扩大OLED面板的数量,同时可能会决定是否将喷墨打印应用于第8.5代(2200×2500mm)OLED面板——这被称为T8项目,于2020年首次发布。

今年9月,TCL华星在德国柏林IFA 2024上曾公开展示了两款IJP(Inkjet Printing,喷墨打印)OLED显示产品,包括14英寸笔记本显示屏和21.6英寸专业显示屏。

TCL华星21.6英寸OLED面板将在其Gen5.5(1300×1500mm)产线上制造,该生产线使用日本JOLED的设备。

5.台积电、英特尔将在IEDM上详细介绍2nm工艺;

今年12月,台积电、IMEC、IBM和三星的研究人员将在旧金山举行的国际电子元件大会(IEDM)上报告垂直堆叠互补场效应晶体管(CFET)的进展。

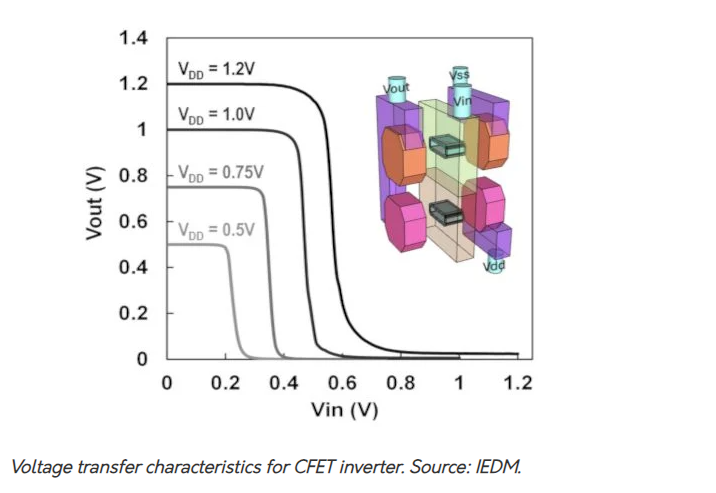

台积电代工厂的S. Liao等工程师发表了一篇论文《首次演示48nm栅极间距单片CFET反相器,面向未来逻辑技术扩展》,介绍了在48nm栅极间距上制造的全功能单片CFET反相器的性能。48nm栅极间距大致相当于5nm工艺。

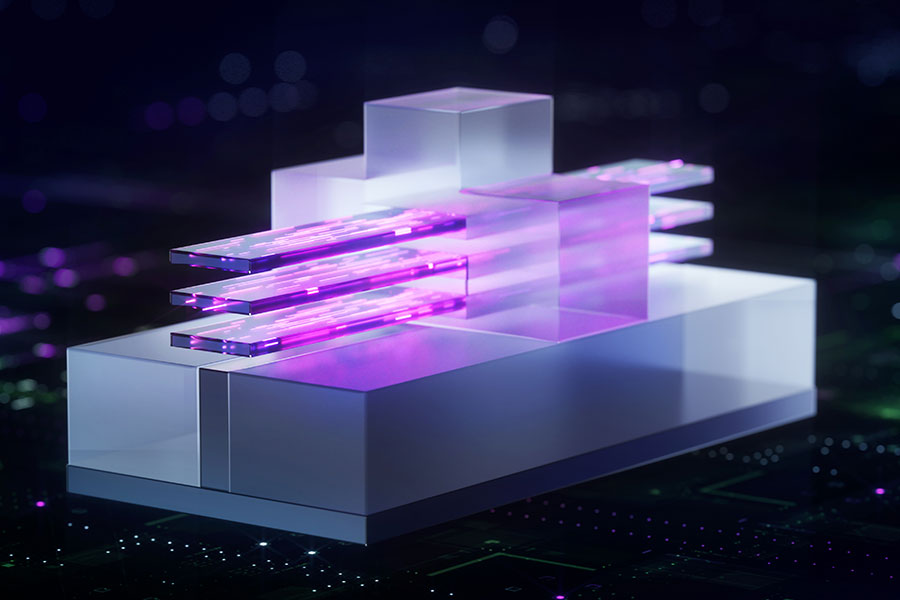

CFET是IMEC研究机构最初提出的概念,被认为是继全栅极场效应晶体管(GAAFET)之后的新一代晶体管架构。

逆变器是由n型纳米片晶体管叠加在p型纳米片晶体管上制成的,这是许多逻辑电路的基本组成部分。台积电的逆变器包括背面触点和互连,以提高性能和增加设计灵活性。

台积电制造的器件表现出高达1.2V的电压传输特性和74~76mV/V的亚阈值斜率(n型和p型器件均如此)。这种高性能CFET被描述为CFET技术进步的里程碑,尽管它不太可能在当代节点投入商业制造。通过双晶体管堆叠实现的面积减小伴随着制造工艺的复杂性,但是以类似于3D-NAND的方式进一步进行尺寸缩放和堆叠可能会带来功率、性能、面积和成本(PPAC)的进步。

论文《双排CFET:面积高效A7技术节点的设计技术协同优化》由IMEC的研究人员提交,表明在z方向和x-y平面上继续将CFET扩展到更高的尺寸方面取得了进展。A7或7埃米技术节点预计将遵循1nm(A10)节点技术。 IMEC自己的路线图曾计划让CFET在2032年左右进入A5(0.5nm)节点的主流生产。

IMEC也参与了使用当代工艺节点的工作。一篇论文讨论了在60nm栅极间距工艺中直接背面接触源极和漏极,大致相当于7nm节点。

IBM和三星也参与了CFET探索,比如论文《面向未来逻辑技术的具有阶梯式通道的单片堆叠FET》,提出了阶梯式结构的概念,其中底部FET通道比上方的通道更宽。这样做的好处是堆叠高度降低,高纵横比工艺带来的挑战更少。本文还讨论了顶部-底部通道中间介电隔离、顶部-底部源极/漏极隔离和双功函数金属。摘要没有讨论金属或栅极间距,因此读者必须等待演示或会议纪要才能了解更多信息。

IEDM会议将于2024年12月7 日至11日在旧金山联合广场希尔顿酒店举行,会议结束后可通过在线方式访问录制内容。(校对/张杰)

6.分析人士:力积电、SBI合资晶圆厂终止建设属意料之中;

力积电(PSMC)与日本金融公司SBI Holdings的半导体合资企业协议最近破裂。力积电表示,董事会已确认停止日本新厂合作计划,并派员前往经产省向主管官员说明,亦已发函告知SBI。SBI于9月底宣布,已终止与力积电在日本建设晶圆厂的合资项目。

力积电强调,该交易是基于Fab IP模式,力积电将提供咨询服务、人员培训和技术转让,以换取日本合作伙伴的服务费和专利费。力积电澄清称,公司没有计划入股或主导新工厂的运营,并声称终止合作不会对其盈利产生影响。

与此同时,力积电表示,将向塔塔集团在印度国内建设的12英寸晶圆厂提供技术,并转移成熟制程技术以及培训印度员工。在业绩恶化的情况下,力积电将集中于资金负担较少的项目。

合资公司仅成立一年多

SBI和力积电双方于2023年8月成立合资公司,随后宣布计划在日本宫城县建设半导体工厂,预计2027年实现汽车半导体量产。总投资额估计约为8000亿日元(约合55亿美元,约合379亿元人民币),日本政府计划在初始投资阶段提供高达1400亿日元的补贴。然而,到2024年3月,力积电已暗示希望减少其在合资公司的股权份额,理由是希望防范风险。正如预期的那样,双方合作在9月底破裂。

力积电表示,SBI向日本经产省申请设厂补贴,并获日本政府支持。但是日本经产省补贴政策规定,获得补贴的厂商需保证新厂必需连续量产10年以上,由于金融业出身的SBI并无半导体产业经验,经产省要求力积电必需共同承担保证责任。另外,力积电为中国台湾股票上市公司,为没有主导性持股的日本新厂保证营运,将违反中国台湾证券交易规定。

对此,SBI董事长Yoshitaka Kitao最近发文,严厉批评力积电的行为。他声称SBI在合作中做出了许多让步,但被单方面放弃,指责力积电背信弃义。日本补助条件已事先说明清楚,并曾与力积电董事长黄崇仁共同会见政府要员。

早已预料到结果

业内人士分析表示,早已预料到该结果,虽然日本方面指责力积电违背承诺,但供应链人士表示,日本可能需要承担一半的责任。

中国台湾晶圆代工业界人士指出,日本以严谨著称,SBI是专业的金融机构,质疑SBI在投资合资公司前,是否充分评估力积电的过去、现在和未来,为何现在才抱怨力积电不靠谱。SBI必须为其内部风险评估机制的失败承担责任。

力积电原为2008年从力晶集团剥离出来的逻辑代工厂,名为钜晶,2018年更名为力积电。2012年12月,力晶退市,激怒30多万股东。经过多年重组,力晶半导体于2019年成为控股公司,并将存储制造业务出售给力积电。

力积电虽然是一家拥有逻辑和存储产品线的晶圆代工厂,但自疫情推动的繁荣消退后,其业绩表现明显不佳。如今,力积电仍是中国台湾四大晶圆代工厂中唯一一家持续亏损的晶圆代工厂。

此外,行业观察人士质疑金融公司SBI进军晶圆代工厂作为其财务战略的可行性。

台积电董事长魏哲家此前曾表示,任何国家或公司要想在半导体技术上实现跨越式发展,并非不可能,但难度极大。跨越式发展往往会导致投资者损失惨重。

业内人士认为,SBI和力积电的合作有点儿戏,在没有经过彻底评估的情况下匆忙宣布联合工厂项目。他们指出,鉴于日本提供的大量补贴,政府自然会设定严格的条件。(校对/张杰)