Cadence 基于 UCIe™ 标准封装 IP 已在 Samsung Foundry 的 5nm 汽车工艺上实现首次流片成功。这一里程碑彰显了Cadence持续提供高性能车规级 IP 解决方案的承诺,可满足新一代汽车电子和高性能计算应用的严格要求。

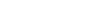

Cadence 的 UCle IP 在 16GT/s 的最高速率及所有支持的更低速率下均实现全功能运行,其眼图质量和误码率(BER)远优于规范要求。该性能验证了设计的稳健性与可靠性,可无缝集成至对能效和可靠性要求严格的汽车电子和数据中心应用场景中。

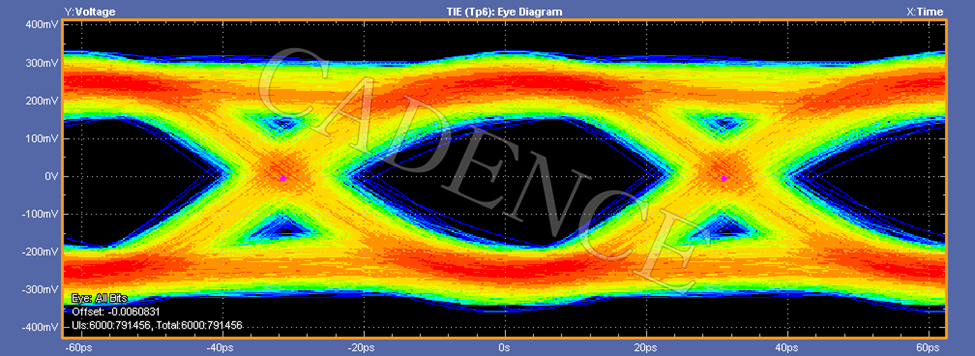

图 1:速度为 16GT/s 时,在所有信道长度下提供卓越的性能,远远超出 UCIe 规范要求

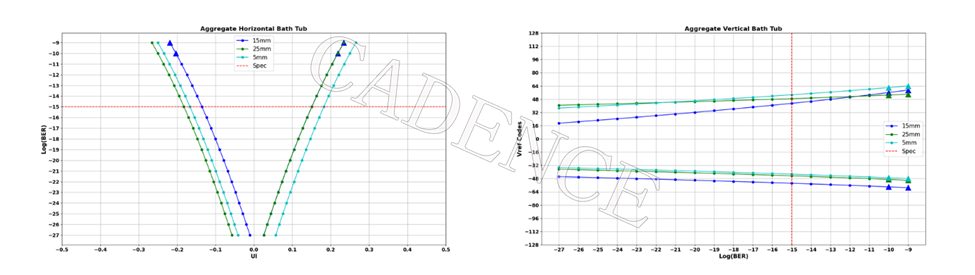

在图 1 的浴盆曲线中,相位插值器(图 1 左图)和 Vref(图 1 右图)在 1e-15 规范要求下的眼图性能(如红色虚线所示)表明,在短、中、最大的裸片间距下,它们都表现出卓越的接收器性能。图 2 显示了使用 PRBS 检查器测量的接收器眼图,PRBS 模式在 UCIe 信道上以最大速度持续传输。基于硬件的成功启动及训练流程使得所有通道均呈现完全打开的眼图。

图 2:对于 16GT/s 下的 PRBS 模式,所有通道显示良好的接收眼图。

PHY 支持 16 Tx 和 16 Rx 标准封装的全双工通信互联,最大距离为 25mm。我们已经在各种距离和布线方法的条件下进行了广泛的测试,以验证其性能。我们的 PHY 可在 Samsung 的 5nm 汽车工艺上实现,符合 UCIe 规范和严格的汽车行业要求。在对于 HPC/AI/ML 应用至关重要的多芯粒设计中,PHY 可在芯粒之间提供低功耗、低延迟的无缝通信,因此可以支持高性能计算(HPC)应用。

图 3:Cadence 是 UCle 的核心成员之一,致力于协助制定包括汽车领域在内的技术规范

我们提供各种配置的 UCIe 控制器产品组合作为 PHY 的补充。从原始流接口到全 PCIe 协议以及轻量级、高效率的 AXI、CXS.B 和 CHI-C2C 接口,Cadence 都能提供支持。我们的控制器产品组合具有多种配置,包括 UCIe-CXS 和 UCIe-AXI,已获得 SGS 的 ASIL-B 车规认证。在交付之前,控制器和 PHY 可无缝合并到 IP 子系统中,并在各级别进行广泛的验证,提供轻松的集成体验,让客户可以专注于 SoC 差异化设计。

我们很高兴能与 Samsung Foundry 持续合作,为双方的共同客户提供业界一流的 IP 解决方案,助力加速创新,将新一代汽车和高性能计算系统推向市场。

图 4:示波器上显示 16GT/s 下的 UCIe Tx 眼图

Cadence将继续推动拓宽互联和系统性能的边界,欲进一步了解 Cadence UCIe 产品更多信息,请点击此处。